Push_response(), Set_command_transaction_mode(), Set_interface_wait_time() – Altera Avalon Verification IP Suite User Manual

Page 66: Push_response() -18, Set_command_transaction_mode() -18, Set_interface_wait_time() -18

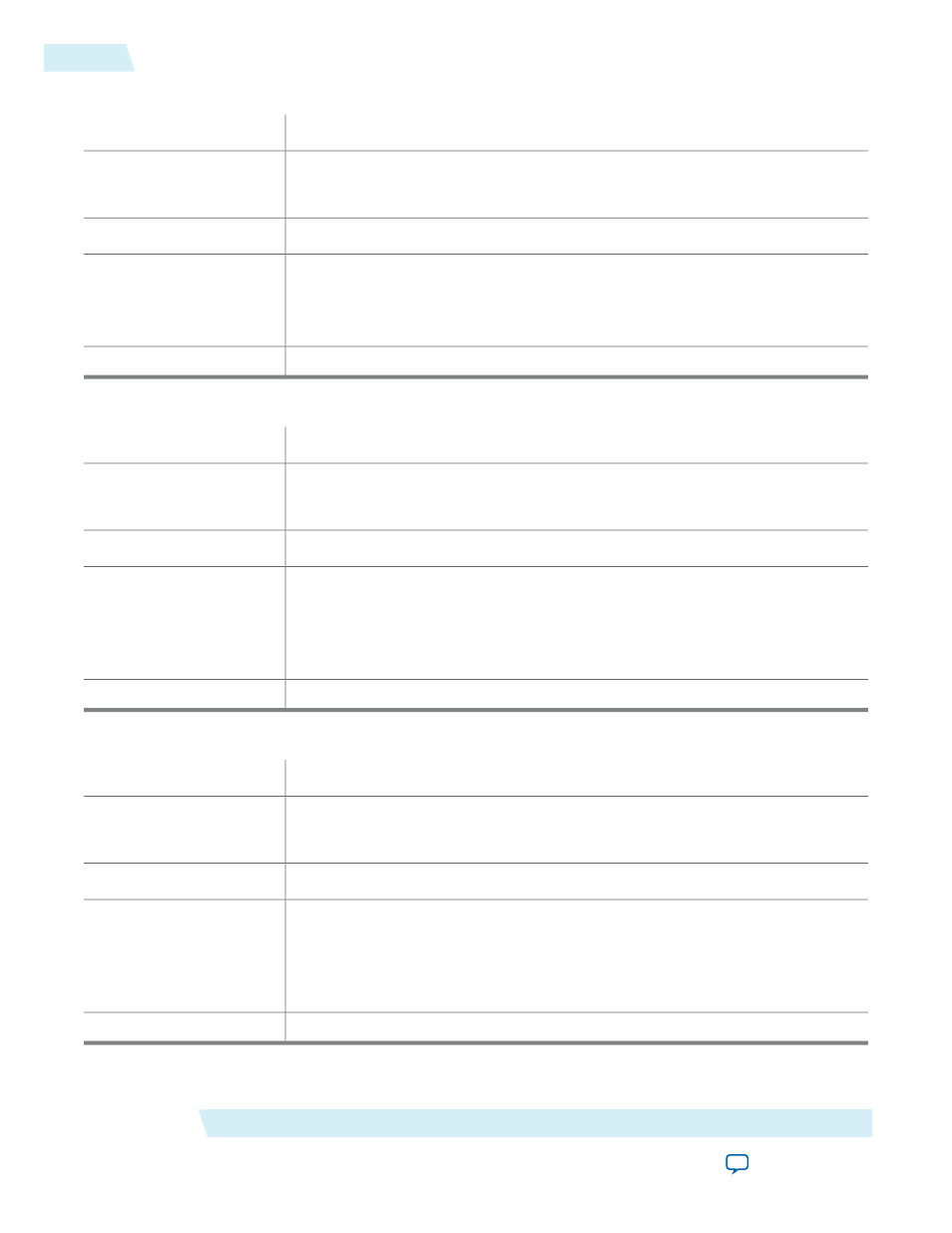

push_response()

void push_response()

Prototype:

Verilog HDL: None

VHDL:

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

Inserts the fully populated response transaction descriptor onto the response

queue. The BFM removes response descriptors from the queue as soon as they

are available. The BFM reads them and drives the Avalon-MM interface response

plane.

Description:

Verilog HDL, VHDL

Language support:

set_command_transaction_mode()

void set_command_transaction_mode (int mode)

;

Prototype:

Verilog HDL:

mode

VHDL:

mode

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

By default, write burst commands are consolidated into a single command

transaction. The single command transaction contains the write data for all burst

cycles in that command. This mode is set when the mode argument equals 0.

When the mode argument is set to 1, the write burst commands yield one command

transaction per burst cycle.

Description:

Verilog HDL, VHDL

Language support:

set_interface_wait_time()

void set_interface_wait_time(int wait_cycles, int index)

Prototype:

Verilog HDL:

wait_cycles

,

index

VHDL:

wait_cycles

,

index

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

Specifies zero or more wait states to assert in each Avalon burst cycle by driving

waitrequest

active. With write burst commands, each write data cycle must wait

the number of cycles corresponding to the cycle index. With read burst commands,

there is only one command cycle corresponding to index 0 which can be forced

to wait.

Description:

Verilog HDL, VHDL

Language support:

Avalon-MM Slave BFM

Altera Corporation

push_response()

6-18