3 switchback, Pmm and peripheral functions, Figure 7-2. internal timing relationships in pmm1 – Maxim Integrated High-Speed Microcontroller User Manual

Page 98: Serial port operation is desired, Table 7-d, Shows the effect of the clo

High-Speed Microcontroller User’s Guide

Rev: 062210

98 of 176

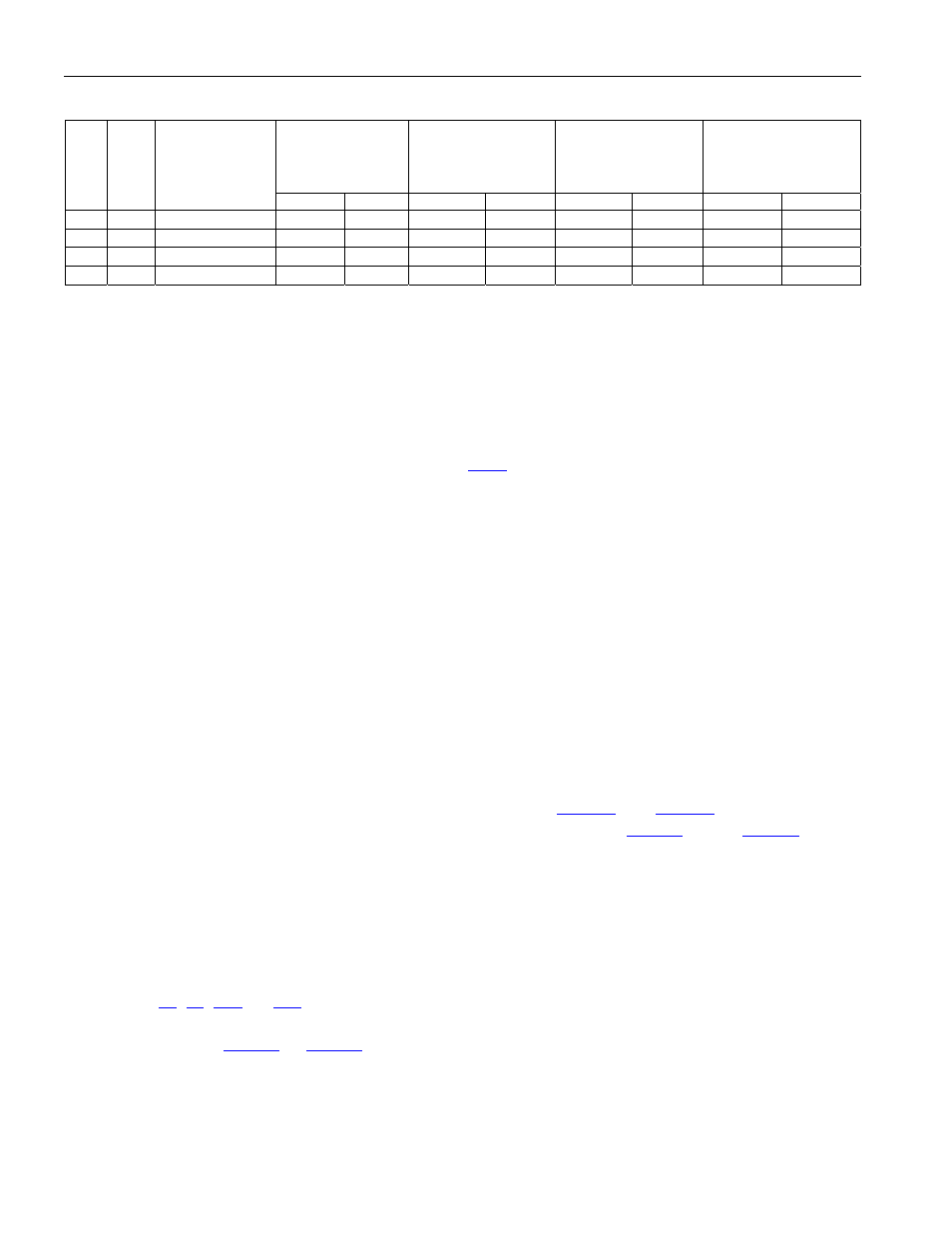

Table 7-D. Effect of Clock Modes on Timer Operation

OSC CYCLES

PER TIMER

0/1/2 CLOCK

OSC CYCLES

PER TIMER 2

CLOCK, BAUD-

RATE GEN.

OSC CYCLES PER

SERIAL PORT

CLOCK MODE 0

OSC CYCLES PER

SERIAL PORT

CLOCK MODE 2

CD1 CD0

OSC CYCLES

PER MACHINE

CYCLE

TxM = 1

TxM = 0

T2M = 1

T2M = 0

SM2 = 0

SM2 = 1

SMOD = 0

SMOD = 1

0

0

Reserved

0 1

4

4

12

2

2

12

4

64

32

0

0 64

(PMM1) 64 192 32 32 3072 64 1024 512

1 1 1024

(PMM2) 1024 3072 512 512 1024 1024 16,348 8192

7.3.3 Switchback

The switchback feature solves one of the most vexing dilemmas faced by power-conscious systems.

Many applications are unable to use the Stop and Idle modes because they require constant computation.

Traditionally, system designers could not reduce the operating speed below that required to process the

fastest event. This meant that system architects would be forced to operate their systems at the highest

rate of speed even when it was not required. The switchback feature allows a system to operate at a

relatively slow speed, and burst to a faster mode when required by an external event. When this feature is

enabled by setting the Switchback Enable bit, SWB, (

.5), a qualified interrupt or serial port reception

or transmission will cause the device to return to divide-by-4 mode. A qualified interrupt is defined as an

interrupt that has occurred and been acknowledged. This means that an interrupt must be enabled and also

not blocked by a higher priority interrupt. After the event is complete, software can manually return the

device to the appropriate PMM. The following sources can trigger a switchback:

External interrupt 0/1/2/3/4/5

Serial start bit detected, serial port 0/1

Transmit buffer loaded, serial port 0/1

Watchdog timer reset

Power-on reset

External reset

In the case of a serial port-initiated switchback, the switchback is not generated by the associated

interrupt. This is because a device operating in PMM will not be able to correctly receive a byte of data to

generate an interrupt. Instead, a switchback is generated by a serial port reception on the falling edge

associated with the start bit, if the associated receiver enable bit (

.4) is set. For serial

port transmissions, a switchback is generated when the serial port buffer (

loaded. This ensures the device will be operating in divide-by-4 mode when the data is transmitted, and

eliminates the need for a write to the CD1, CD0 bits to exit PMM before transmitting. The switchback

feature is unaffected by the state of the serial port interrupt flags (RI_0, TI_0, RI_1, TI_1).

The timing of the switchback is dependent on the source. Interrupt-initiated switchbacks will occur at the

start of the first C1 cycle following the event initiating the switchback. In PMM, each internal Cx cycle is

16 external clock cycles for PMM1 and 256 cycles for PMM2. If the current instruction in progress is a

write to the

registers, interrupt processing will be delayed until the completion of the

following instruction. Serial transmit-initiated switchbacks occur at the start of the instruction following

the MOV that loads

. Serial reception-initiated switchbacks occur during the Cx cycle

in which the falling edge was detected. There are a few points that must be considered when using a serial

port reception to generate a switchback. Under normal circumstances, noise on the line or an aborted

transmission would cause the serial port to timeout and the data to be ignored. This presents a problem if

the switchback is used, however, because a switchback would occur but there is no indication to the