33 status register (status), Status, 4) and xtoff – Maxim Integrated High-Speed Microcontroller User Manual

Page 45

High-Speed Microcontroller User’s Guide

Rev: 062210

45 of 176

4.2.33

Status Register (STATUS)

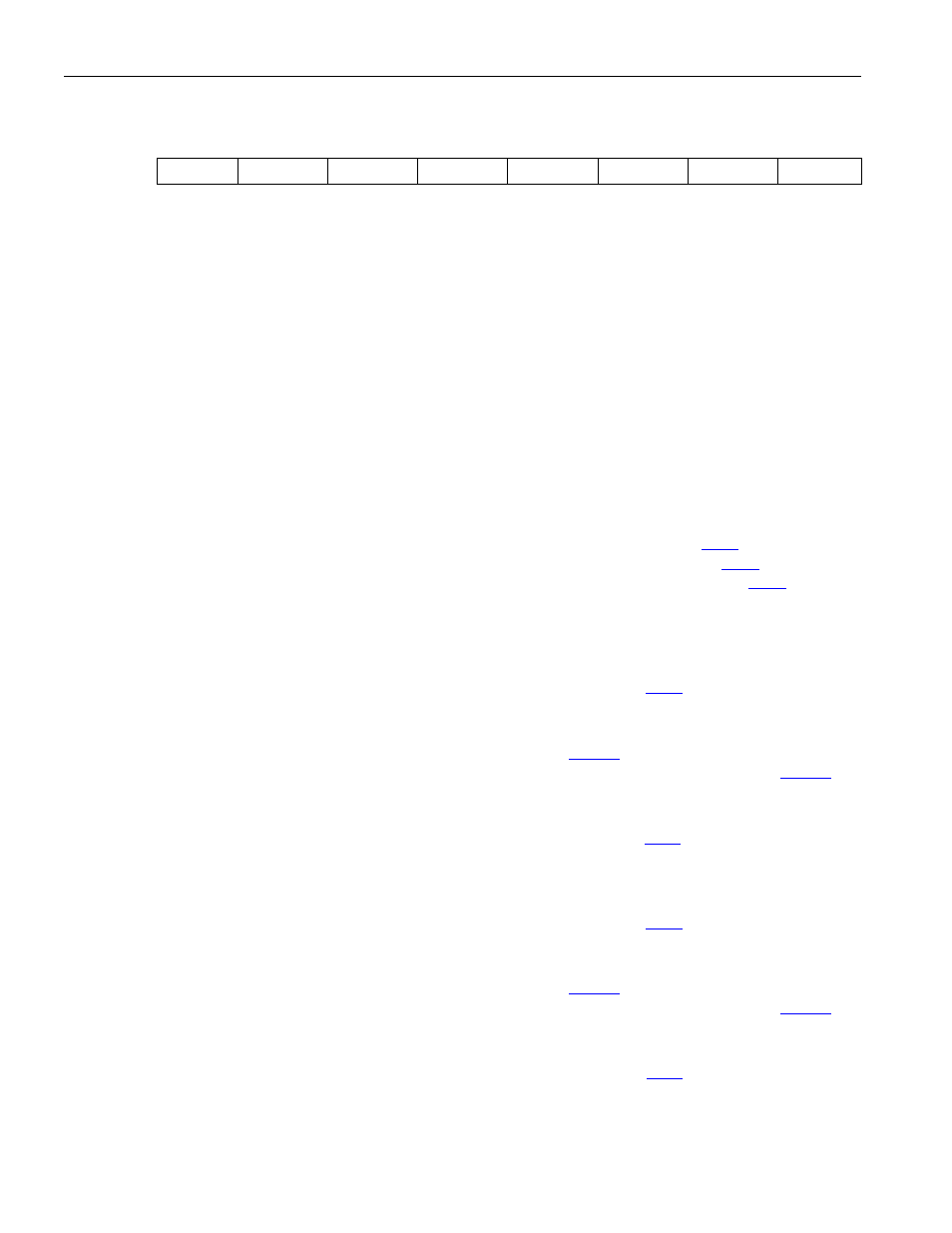

7 6 5 4 3 2 1 0

SFR C5h

PIP

HIP

LIP

XTUP SPTA1 SPRA1

SPTA0 SPRA0

R-0 R-0 R-0 R-0* R-0 R-0

R-0 R-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset, * = See description

PIP

Bit 7

Power-Fail Priority Interrupt Status. When set, this bit indicates that software is

currently servicing a power-fail interrupt. It is cleared when the program executes the

corresponding RETI instruction. This bit is indeterminate on devices that do not

incorporate the power-fail interrupt.

HIP

Bit 6

High Priority Interrupt Status. When set, this bit indicates that software is currently

servicing a high priority interrupt. It is cleared when the program executes the

corresponding RETI instruction.

LIP

Bit 5

Low Priority Interrupt Status. When set, this bit indicates that software is currently

servicing a low priority interrupt. It is cleared when the program executes the

corresponding RETI instruction.

XTUP

Bit 4

Crystal Oscillator Warmup Status. This bit indicates whether the CPU crystal

oscillator has completed the 65,536 cycle warmup and is ready to operate from the

external crystal or oscillator. This bit is cleared each time the crystal oscillator is

restarted following an exit from Stop mode or the XTOFF bit (

cleared, this bit prevents software from setting the XT/

RG bit (

operation from the crystal. Note that XTUP differs from the RGMD bit (

.2) in that

XTUP shows the status of the crystal while RGMD shows the current clock source. This

bit is set to 1 following a power–on reset, but is unaffected by other forms of reset.

SPTA1

Bit 3

Serial Port 1 Transmit Activity Monitor. When set, this bit indicates that data is

currently being transmitted by serial port 1. It is cleared when the internal hardware sets

the TI_1 bit. Do not alter the Clock Divide Control bits (

or serial port data may be lost.

On the DS8xC520 and DS8xC530, this bit does not accurately indicate serial port 1

transmit activity if a character is written to

while TI_1 is high. If software

intends to poll this bit, first clear the TI_1 bit before writing each character to

.

SPRA1

Bit 2

Serial Port 1 Receive Activity Monitor. When set, this bit indicates that data is

currently being received by serial port 1. It is cleared when the internal hardware sets

the RI_1 bit. Do not alter the Clock Divide Control bits (

or serial port data may be lost.

SPTA0

Bit 1

Serial Port 0 Transmit Activity Monitor. When set, this bit indicates that data is

currently being transmitted by serial port 0. It is cleared when the internal hardware sets

the TI_1 bit. Do not alter the Clock Divide Control bits (

or serial port data may be lost.

On the DS8xC520 and DS8xC530, this bit does not accurately indicate serial port 0

transmit activity if a character is written to

while TI_0 is high. If software

intends to poll this bit, first clear the TI_0 bit before writing each character to

.

SPRA0

Bit 0

Serial Port 0 Receive Activity Monitor. When set, this bit indicates that data is

currently being received by serial port 0. It is cleared when the internal hardware sets

the RI_1 bit. Do not alter the Clock Divide Control bits (

or serial port data may be lost.