2 pmm and peripheral functions, Power management mode timing, Table 7-c. power management and status bit summary – Maxim Integrated High-Speed Microcontroller User Manual

Page 97

High-Speed Microcontroller User’s Guide

Rev: 062210

97 of 176

timers (including serial port baud-rate generation), watchdog timer, and software timing loops will also

run at the reduced speed. Most applications will not find it necessary to attend to this much detail, but the

information is provided for calculating critical timings.

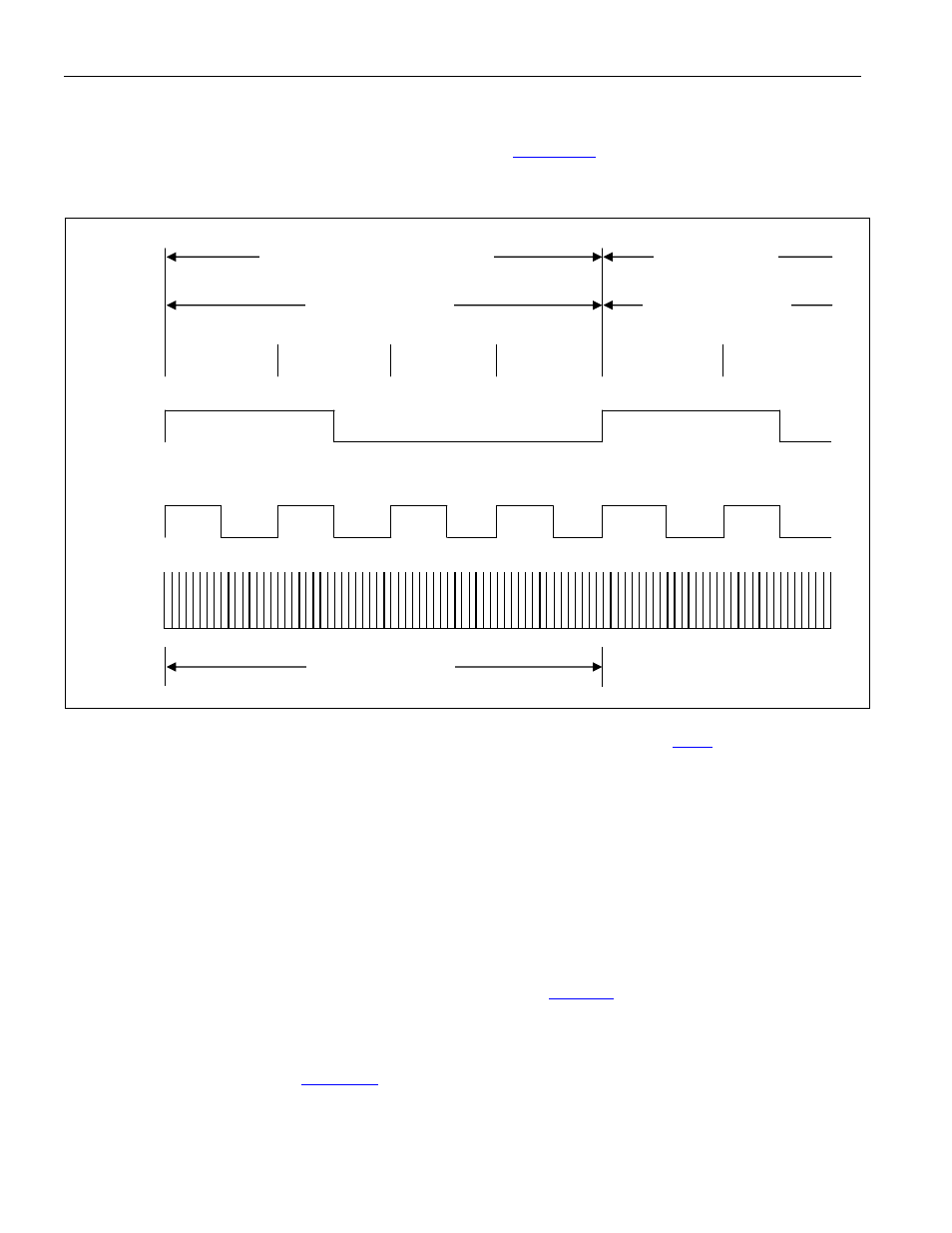

demonstrates the internal timing

relationships during PMM1.

Figure 7-2. Internal Timing Relationships in PMM1

PMM1 and PMM2 are entered and exited by setting the

Cloc

.7-6). In addition, it

is possible use the switchback feature to affect a return to the divide-by-4 mode from either power

management mode. This allows both hardware and software to cause an exit from PMM. Entry to or exit

from either PMM must be by the divide-by-4 mode. This means that to switch from divide-by-64 to

divide-by-1024 and vice versa, one must first switch back to divide-by-4 mode. Attempts to execute an

illegal speed change will be ignored and the bits will remain unchanged. It is the responsibility of the

software to test for serial port activity before attempting to change speed, as a modification of the clock

divider bits during a serial port operation will corrupt the data.

7.3.2 PMM and Peripheral Functions

Timers 0, 1, and 2 will default on reset to a 12 clock per cycle operation to remain compatible with the

original 8051 timing. The timers can be individually configured to run at machine cycle timing (divide-

by-4) by setting the relevant bits in the Clock Control Register (

;8Eh). Because the timers derive

their time base from the internal clock, timers 0, 1, and 2 operate at reduced clock rates during PMM.

This will also affect the operation of the serial ports in PMM. In general, it is not possible to generate

standard baud rates while in PMM, and the user is advised to avoid PMM or use the switchback feature if

serial port operation is desired.

shows the effect of the clock divider value on timer operation.

INTERNAL

CLOCK

(PMM1)

SINGLE-CYCLE INSTRUCTION

ALE

SINGLE-CYCLE

INSTRUCTION

MACHINE CYCLE

MACHINE CYCLE

EXTERNAL

CLOCK

MACHINE

CYCLES

64 CLOCK CYCLES

C1

C2

C3

C4

C1

C2