1 system control byte description (eprom; fffch), Power management register (pmr) – Maxim Integrated High-Speed Microcontroller User Manual

Page 44

High-Speed Microcontroller User’s Guide

Rev: 062210

44 of 176

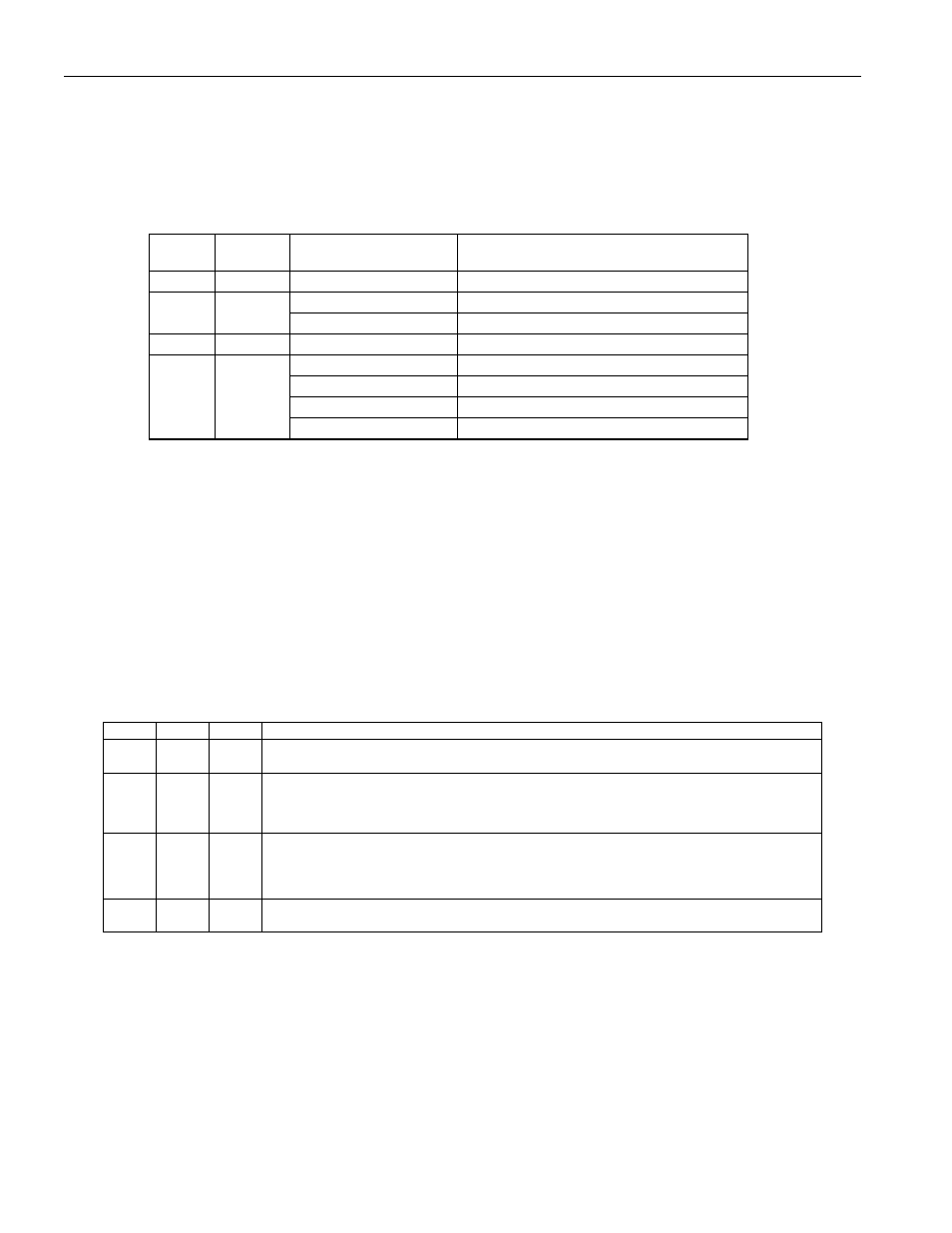

DME1, DME0

Bits 1, 0

Data Memory Enable 1-0. These bits determine the functional relationship of the first

1024 bytes of data memory. Three memory configurations are supported to allow either

external data memory access through the expanded multiplexed address/data bus of

Ports 0 and Port 2, internal SRAM data memory access, or read-only access to EPROM

programming information. Note these bits are cleared after a reset, so access to the

internal SRAM is prohibited until these bits are modified.

DME1 DME0

DATA MEMORY

ADDRESS RANGE

MEMORY ACCESS

0 0 0000h–FFFFh

External Data Memory (default)

0000h–03FFh

Internal SRAM Data Memory

0 1

0400h–FFFFh

External Data Memory

1 0

Reserved Reserved

0000h–03FFh

Internal SRAM Data Memory

0400h–FFFBh

Reserved

FFFCh

System Control Byte (EPROM Read Only)

1 1

FFFDh–FFFFh

Reserved

4.2.32.1

System Control Byte Description (EPROM; FFFCh)

The System Control Byte is a special EPROM location that contains nonvolatile system

information. This byte is set during EPROM programming and is not alterable by

software. This register can only be read when both Data Memory Enable bits are set.

The user must be sure that this location is programmed by a special programming utility

supplied with the programming device.

Bits 7–3

Reserved. These bits will read 1. These bits should be set to 1 during EPROM

programming.

LB3, LB2, LB1

Bits 2, 1, 0

EPROM Program Lock Bit 3 to 1. These bits show the status of the firmware security

of the on-board EPROM. Bit combinations other than shown are illegal.

LB3 LB2 LB1

EPROM

PROTECTION

MODE

0 0 0

Unconditional verification, full external operation. Additional EPROM programming allowed

without full device erasure.

0 0 1

Verification using encryption, execution of external MOVC instruction on internal program

memory is disabled. All other program execution and data memory access allowed. Device must

be fully erased before EPROM can be programmed again.

0 1 1

Verification disabled, execution of external MOVC instruction on internal program memory is

disabled, and access to internal MOVX data from external program is prohibited. All other

program execution and data memory access allowed. Device must be fully erased before

EPROM can be programmed again.

1 1 1

Verification disabled, external program execution prohibited. Device must be fully erased before

EPROM can be programmed again.