7 comparison to the 8051, Figure 5-6. four-cycle instruction timing – Maxim Integrated High-Speed Microcontroller User Manual

Page 71

High-Speed Microcontroller User’s Guide

Rev: 062210

71 of 176

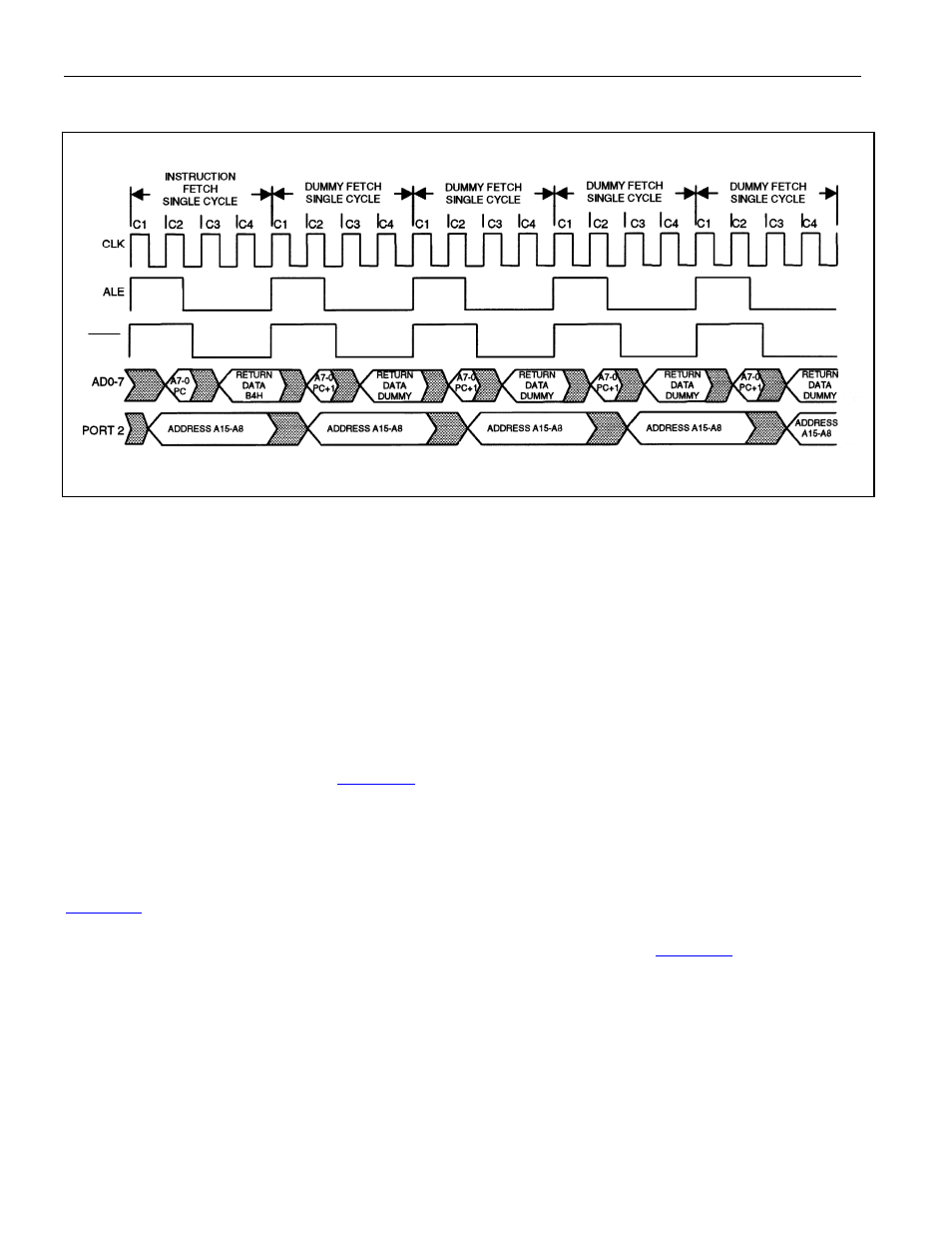

Figure 5-7. Five-Cycle Instruction Timing

Example: MUL A,B

A4h

*Shaded areas are held in a weak latch on the port until overdriven.

5.7 Comparison to the 8051

The original 8051 had a 12-clock architecture. A machine cycle needed 12 clocks and most instructions

were either one or two machine cycles. Thus except for the MUL and DIV instructions, the 8051 used

either 12 or 24 clocks for each instruction. Furthermore, each cycle in the 8051 used two memory fetches.

In many cases the second fetch was a dummy, and the extra clock cycles were wasted.

The high-speed microcontroller uses 4 clocks per cycle. Since a cycle is now aligned with a memory fetch

when possible, most instructions have the same number of cycles as bytes. This leads to more

“categories” than the original 8051. Where there were primarily one and two cycle instructions before,

there are now one, two, three, and four-cycle instructions. Multiply and Divide require five cycles. Note

however, that regardless of the number of cycles, each instruction is at least 1.5 and most are 2 to 3 times

faster than its original counterpart.

shows each instruction, the number of clocks used in the

high-speed microcontroller and the number used in the 8051 for comparison. The factor by which the

high-speed microcontroller improves on the 8051 is shown as the Speed Advantage. A Speed Advantage

of 3.0 means that the high-speed microcontroller performs the same instruction three times faster that the

8051.

provides a summary by instruction type. Note that many of the instructions provide multiple op

codes. As an example, the ADD A, Rn instruction can act on one of 8 working registers. There are 8 op

codes for this instruction because it can be used on 8 independent locations.

shows totals for

both number of instructions and number of op codes. Averages are provided in the tables. However, the

real speed improvement seen in any system will depend on the instruction mix. Programs that use

immediate or direct data combined with the accumulator or working registers will be improved the least.

These are two cycle, two-byte instructions. Moderate performance improvement will be gained by

emphasizing short branches and instructions that use only direct and immediate data (no accumulator or

working register). These instructions tend to be three cycle instructions. The largest number of

improvements come from the single cycle instructions involving only the accumulator and working

registers. Also, the two-cycle data movement instructions involving the working registers are greatly

improved.

PSEN