32 power management register (pmr), Rom size select (romsize), 3) m – Maxim Integrated High-Speed Microcontroller User Manual

Page 43

High-Speed Microcontroller User’s Guide

Rev: 062210

43 of 176

4.2.32

Power Management Register (PMR)

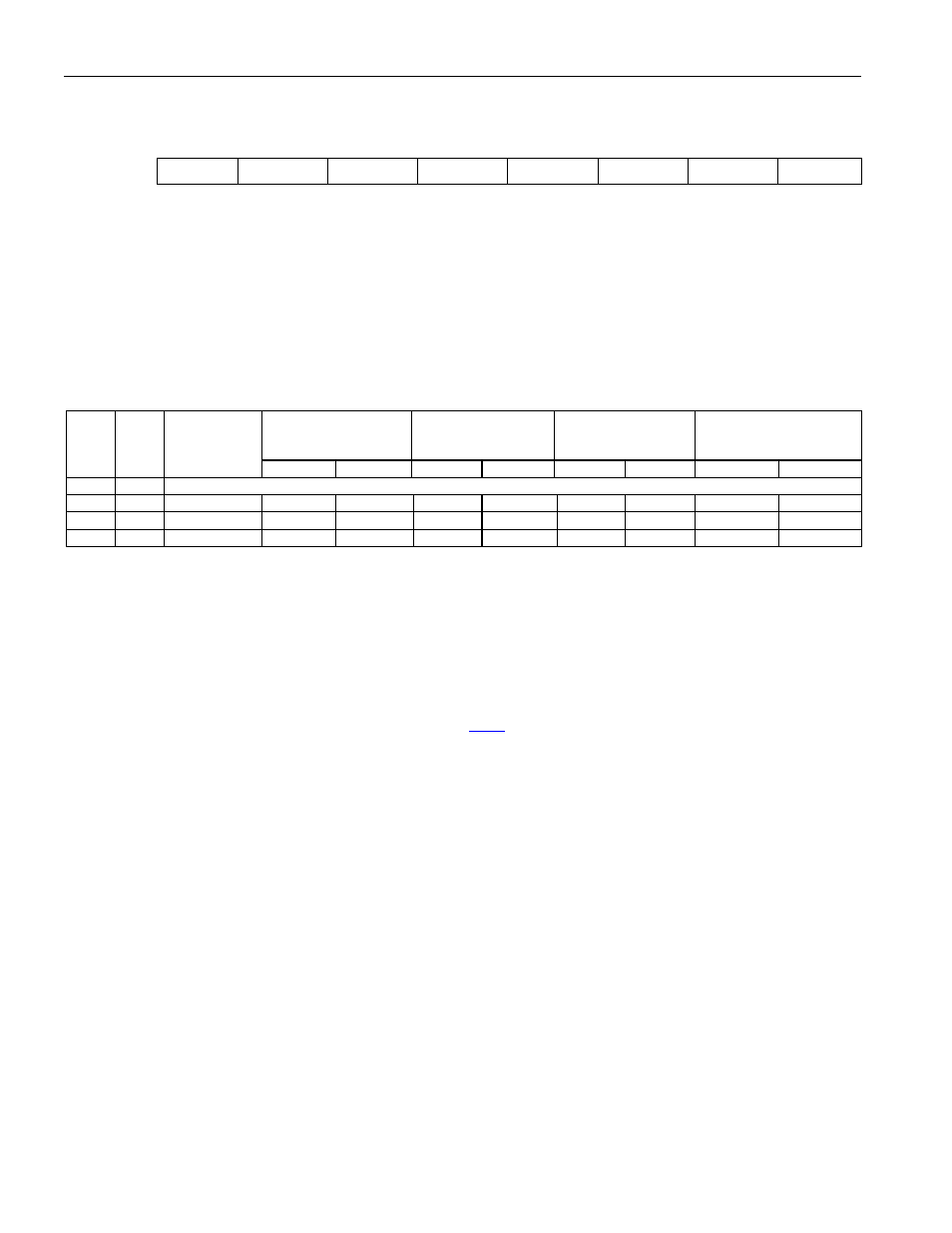

7 6 5 4 3 2 1 0

SFR C4h

CD1

CD0

SWB

— XTOFF

ALEOFF

DME1

DME0

RW-0

RW-1

RW-0

RW*-0

RW-0

RW-0

RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset, * = See description

CD1, CD0

Bits 7, 6

Clock Divide Control 1-0. These bits select the number of crystal oscillator clocks

required to generate one machine cycle. Switching between modes requires a transition

through the divide-by-4 mode (CD1, CD0 = 01). For example, to go from 64 to 1024

clocks per cycle the device must first go from 64 to 4 clocks per cycle, and then from 4

to 1024 clocks per cycle. Attempts to perform an invalid transition will be ignored. The

setting of these bits will affect the timers and serial ports as shown below.

OSC CYCLES PER

TIMER 2 CLK,

BAUD-RATE GEN.

OSC CYCLES PER

SERIAL PORT

CLK, MODE 0

OSC CYCLES PER

TIMER 2 CLK,

BAUD-RATE GEN.

OSC CYCLES PER

SERIAL PORT CLK,

MODE 2

CD1 CD0

OSC

CYCLES

PER MACH.

CYCLE

TxM = 0

TxM = 1

T2M = 0

T2M = 1

SM2 = 0

SM2 = 1

SDMO = 0

SMOD = 1

0 0

RESERVED

0 1

4

12

4

2

2

12

4

64

32

1 0

64

192

64

32

32 194 64 1024

512

1 1 1024

3072 1024 512 512 3072 1024 16384 8192

SWB

Bit 5

Switchback Enable. This bit allows an enabled external interrupt or serial port activity

to force the Clock Divide Control bits to the divide-by-4 state (01). Upon internal

acknowledgement of an external interrupt, the device will switch modes at the start of

the jump to the interrupt service routine. Note that this means that an external interrupt

must actually be recognized (i.e., be enabled and not masked by higher priority

interrupts) for the switchback to occur. For serial port reception, the switch occurs at the

start of the instructions following the falling edge of the start bit.

Bit 4

Reserved. When modifying the

register, software must write a 0 to this bit. Read

data will be indeterminate.

XTOFF

Bit 3

Crystal Oscillator Disable. This bit disables the CPU crystal oscillator. It can only be

set to 1 while running the ring oscillator (XT/

RG = 0). Clearing this bit restarts the

crystal amplifier, reset the crystal warmup counter, and after 65,536 external crystal

cycles the XTUP bit will be set.

0 = Crystal oscillator is enabled.

1 = Crystal oscillator is disabled.

ALEOFF

Bit 2

ALE Disable. This bit disables the expression of the ALE signal on the device pin

during all on-board program and data memory accesses. External memory accesses will

automatically enable ALE independent of ALEOFF.

0 = ALE expression is enabled.

1 = ALE expression is disabled.