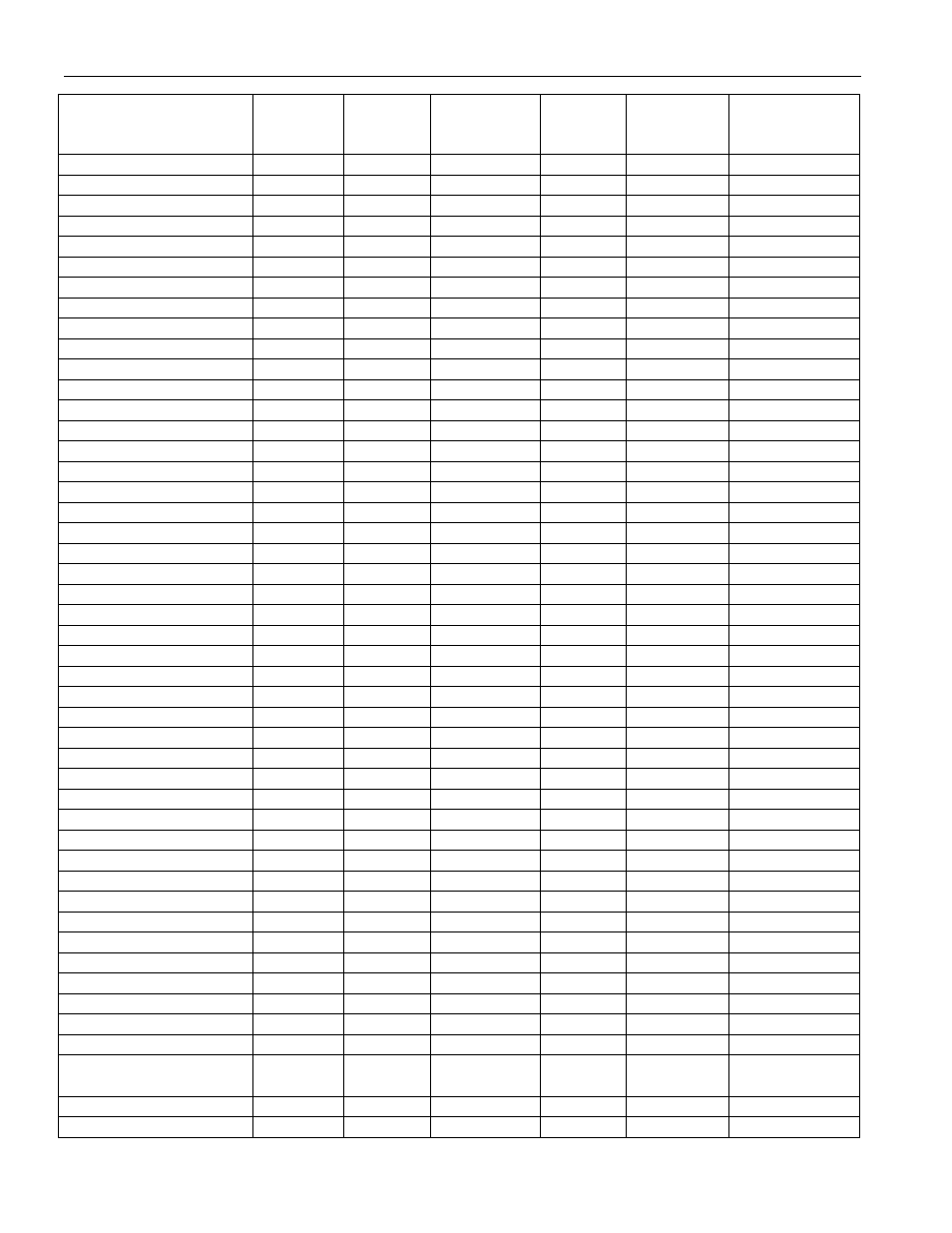

Table 5-a. instruction timing comparison – Maxim Integrated High-Speed Microcontroller User Manual

Page 73

High-Speed Microcontroller User’s Guide

Rev: 062210

73 of 176

INSTRUCTION

HEX

CODE

HSM

CLOCK

CYCLES

HSM TIME

at 25MHz

8051

CLOCK

CYCLES

8051 TIME

at 25MHz

HSM vs. 8051

SPEED

ADVANTAGE

RR A

03

4

160ns

12

480ns

3

RRC A

13

4

160ns

12

480ns

3

SWAP A

C4

4

160ns

12

480ns

3

MOV A, Rn

E8..EF

4

160ns

12

480ns

3

MOV A, direct

E5

8

320ns

12

480ns

1.5

MOV A, @Ri

E6..E7

4

160ns

12

480ns

3

MOV A, #data

74

8

320ns

12

480ns

1.5

MOV Rn, A

F8..FF

4

160ns

12

480ns

3

MOV Rn, direct

A8..AF

8

320ns

24

960ns

3

MOV Rn, #data

78..7F

8

320ns

12

480ns

1.5

MOV direct, A

F5

8

320ns

12

480ns

1.5

MOV direct, Rn

88..8F

8

320ns

24

960ns

3

MOV direct, direct

85

12

480ns

24

960ns

2

MOV direct, @Ri

86..87

8

320ns

24

960ns

3

MOV direct, #data

75

12

480ns

24

960ns

2

MOV @Ri, A

F6..F7

4

160ns

12

480ns

3

MOV @Ri, direct

A6..A7

8

320ns

24

960ns

3

MOV @Ri, #data

76..77

8

320ns

12

480ns

1.5

MOV DPTR, #data 16

90

12

480ns

24

960ns

2

MOVC A, @A+DPTR

93

12

480ns

24

960ns

2

MOVC A, @A+PC

83

12

480ns

24

960ns

2

MOVX A, @Ri

E2..E3

8

320ns

24

960 ns

3

MOVX A, @DPTR

E0

8

320ns

24

960ns

3

MOVX @Ri, A

F2..F3

8

320ns

24

960ns

3

MOVX @DPTR, A

F0

8

320ns

24

960ns

3

PUSH direct

C0

8

320ns

24

960ns

3

POP direct

D0

8

320ns

24

960ns

3

XCH A, Rn

C8..CF

4

160ns

12

480ns

3

XCH A, direct

C5

8

320ns

12

480ns

1.5

XCH A, @Ri

C6..C7

4

160ns

12

480ns

3

XCHD A, @Ri

D6..D7

4

160ns

12

480ns

3

CLR C

C3

4

160ns

12

480ns

3

CLR bit

C2

8

320ns

12

480ns

1.5

SETB C

D3

4

160ns

12

480ns

3

SETB bit

D2

8

320ns

12

480ns

1.5

CPL C

B3

4

160ns

12

480ns

3

CPL bit

B2

8

320ns

12

480ns

1.5

ANL C, bit

82

8

320ns

24

960ns

3

ANL C,

bit

B0 8 320ns 24 960ns 3

ORL C, bit

2

8

320ns

24

960ns

3

ORL C,

bit

A0 8 320ns 24 960ns 3

MOV C, bit

A2

8

320ns

12

480ns

1.5

MOV bit, C

92

8

320ns

24

960ns

3

ACALL addr 11

Hex code

Hex codes = 11, 31, 51,

71, 91, B1, D1, or F1

Byte 1

12

480ns

24

960ns

2

LCALL addr 16

12

16

640ns

24

960ns

1.5

RET

22

16

640ns

24

960ns

1.5