3 three-cycle instructions, Figure 5-3. single-cycle instruction timing, N is shown in – Maxim Integrated High-Speed Microcontroller User Manual

Page 67: Figure 5-4

High-Speed Microcontroller User’s Guide

Rev: 062210

67 of 176

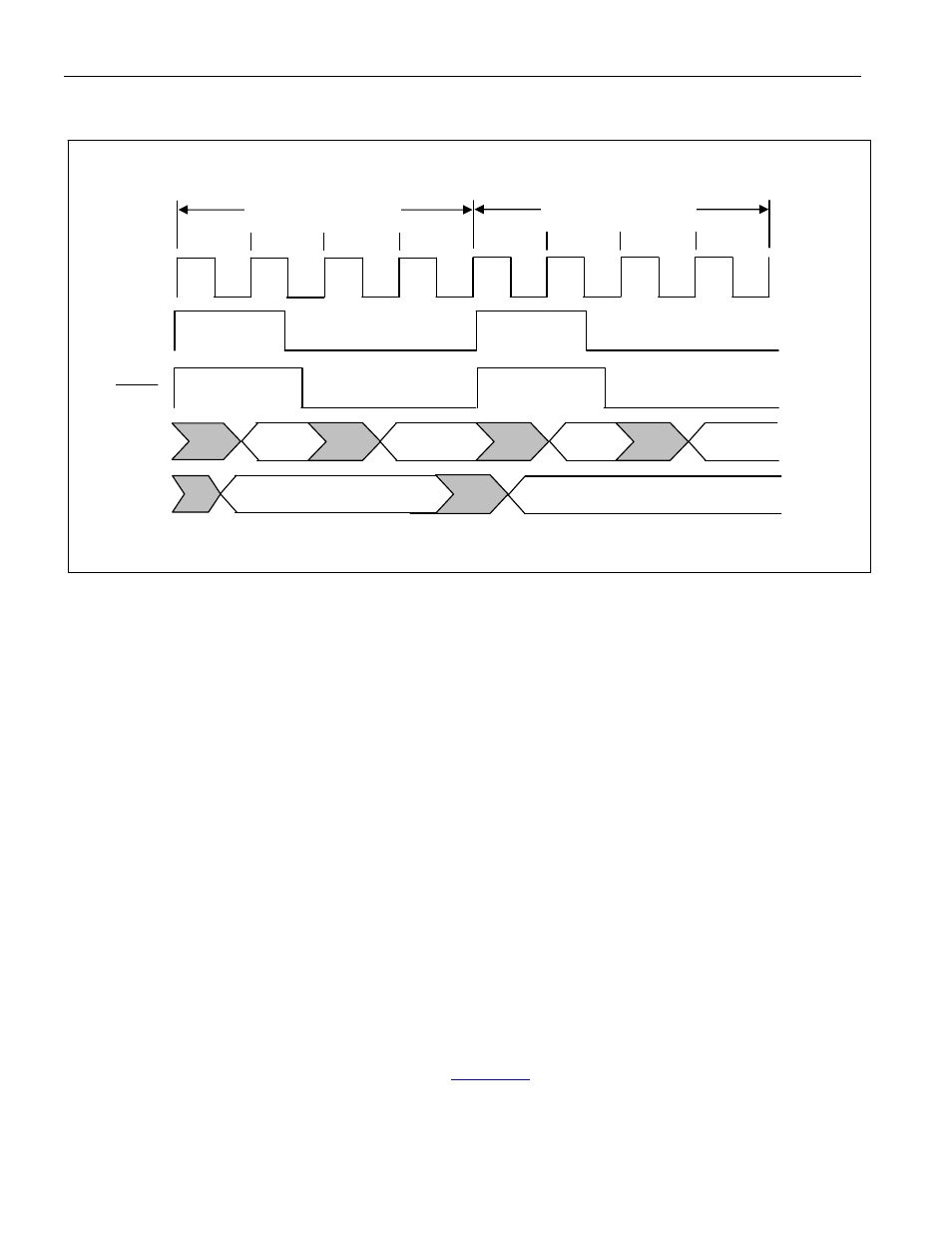

Figure 5-4. Two-Cycle Instruction Timing

Example: ANL A, direct: 55h addr7-0

5.6.3 Three-Cycle Instructions

Three-cycle instructions come in two varieties. The first requires three memory accesses. These are

similar to one and two cycle instructions in that the number of bytes equals the number of cycles.

The second variety is a three-cycle instruction that simply requires 12 clocks to perform the function.

This may have one or two bytes. Examples of both types are shown below.

ANL direct, #data

53h

(3

bytes)

a

7

–a

0

d7–d0

SJMP rel

80h

(2

bytes)

a

7

–a

0

INC DPTR

A3h

(1

byte)

In the first example, the first memory fetch is the op code. The second is the location of the destination

register. The third memory fetch is the operand that is used by the instruction. This instruction has three

memory accesses, so it requires three machine cycles. The second example has the operand in the first

byte and the jump location in the second. It requires three cycles to actually perform the jump. The third

example contains simply the op code, which is 1 byte. This instruction involves the manipulation of a 16-

bit register so it takes longer than 8-bit operations.

shows the timing of all three types of three

cycle instructions.

CLK

ALE

PSEN

AD0-7

PORT2

A7-0

PIC

C3

C1

C2

C4

C3

C1

C2

C4

RETURN

DATA

ADDRESS A15-A8

INSTRUCTION FETCH

SINGLE CYCLE

OPERAND FETCH

SINGLE CYCLE

ADDRESS A15-A8

A7-0

PC+1

RETURN DATA OPER

AND ADDRESS 7-0

*Shaded areas are held in a weak latch on the port until overdriven.