50 extended interrupt priority (eip), Real-time alarm second register (rtas), Real-time alarm minute register (rtam) – Maxim Integrated High-Speed Microcontroller User Manual

Page 54: Real-time alarm hour register (rtah)

High-Speed Microcontroller User’s Guide

Rev: 062210

54 of 176

4.2.50

Extended Interrupt Priority (EIP)

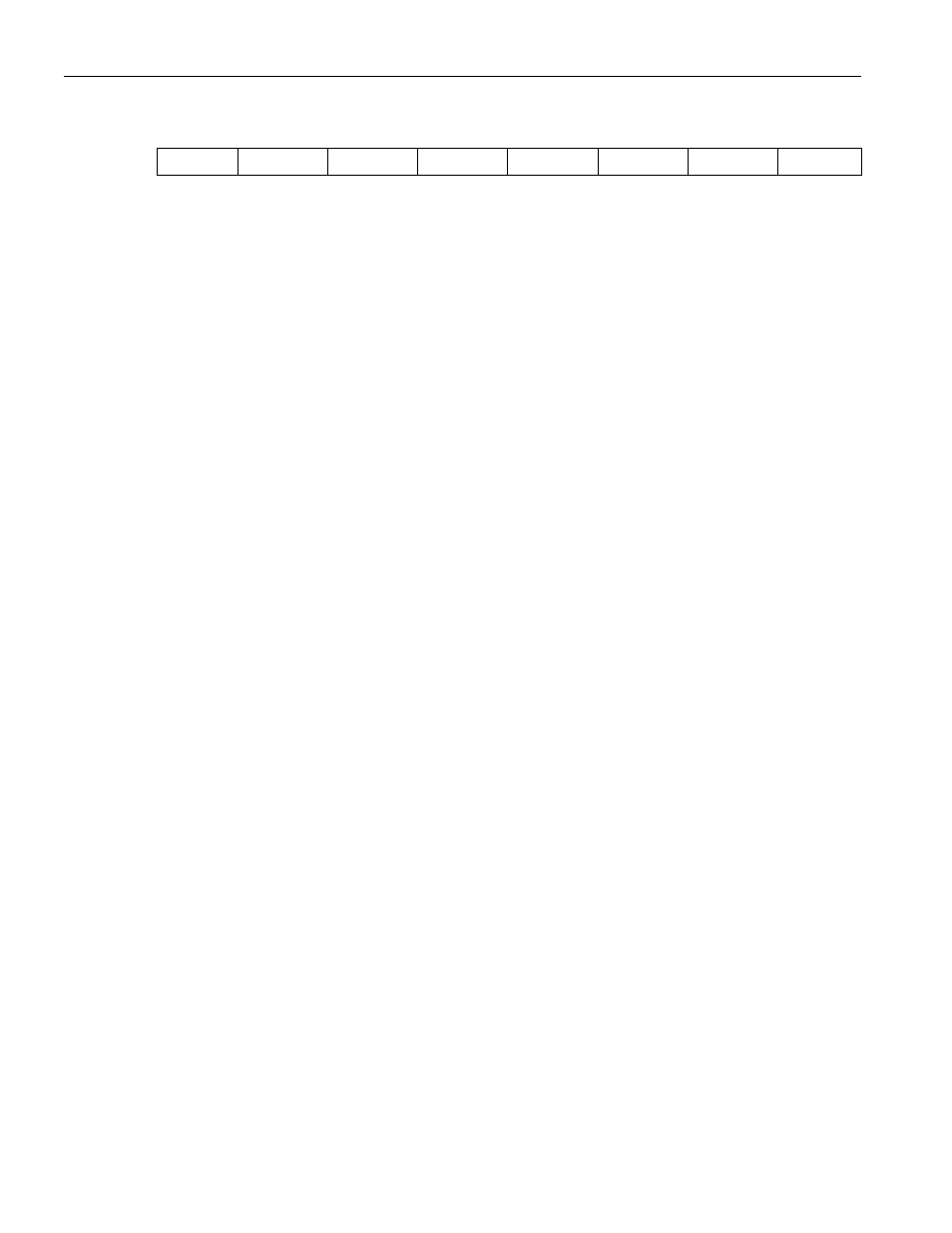

7 6 5 4 3 2 1 0

SFR F8h

—

—

PRTCI

PWDI PX5 PX4

PX3 PX2

RW-0 RW-0 RW-0 RW-0

RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

Bits 7, 6

Reserved. These bits will be 0 when read.

PRTCI

Bit 5

Real-Time Clock Interrupt Priority. This bit controls the priority of the real–time

clock interrupt on the DS87C530. This bit will read 0 on all other devices.

0 = The real-time clock interrupt is a low priority interrupt.

1 = The real-time clock interrupt is a high priority interrupt.

PWDI

Bit 4

Interrupt Priority. This bit controls the priority of the watchdog interrupt.

0 = The watchdog interrupt is a low priority interrupt.

1 = The watchdog interrupt is a high priority interrupt.

PX5

Bit 3

External Interrupt 5 Priority. This bit controls the priority of external interrupt 5.

0 = External interrupt 5 is a low priority interrupt.

1 = External interrupt 5 is a high priority interrupt.

PX4

Bit 2

External Interrupt 4 Priority. This bit controls the priority of external interrupt 4.

0 = External interrupt 4 is a low priority interrupt.

1 = External interrupt 4 is a high priority interrupt.

PX3

Bit 1

External Interrupt 3 Priority. This bit controls the priority of external interrupt 3.

0 = External interrupt 3 is a low priority interrupt.

1 = External interrupt 3 is a high priority interrupt.

PX2

Bit 0

External Interrupt 2 Priority. This bit controls the priority of external interrupt 2.

0 = External interrupt 2 is a low priority interrupt.

1 = External interrupt 2 is a high priority interrupt.