3 program memory interconnect, Romsize feature, Table 6-a. data memory access control – Maxim Integrated High-Speed Microcontroller User Manual

Page 78: Shown in, Table 6-b, Note that the mem

High-Speed Microcontroller User’s Guide

Rev: 062210

78 of 176

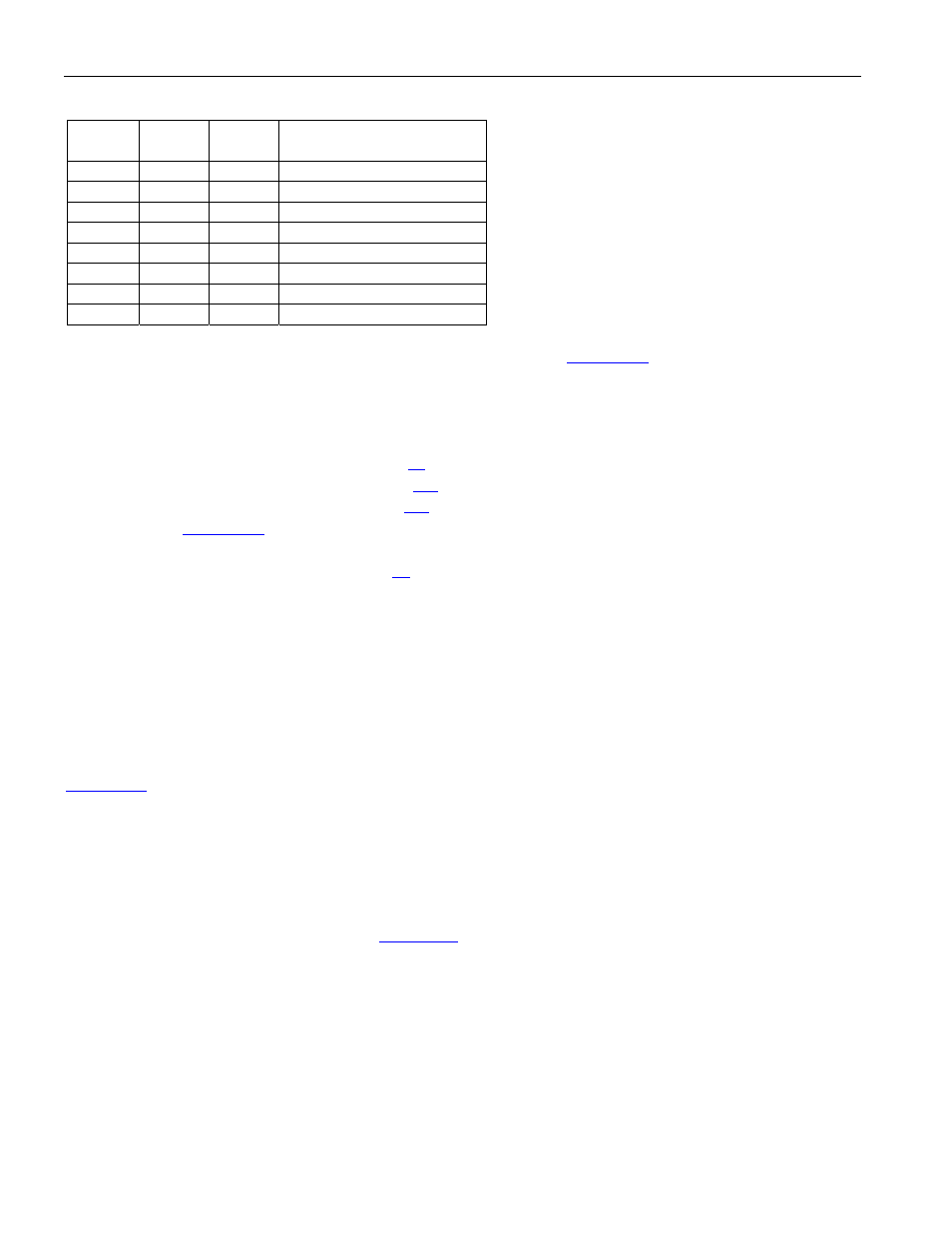

Table 6-B. ROMSIZE Register Settings

RMS2 RMS1 RMS0

MAX ON-CHIP ROM

(kB)

0 0 0

0

0 0 1

1

0 1 0

2

0 1 1

4

1 0 0

8

1 0 1

16

1 1 0

32

1 1 1

64

After reset, a device with internal program memory will reset the

bits to their default setting.

This will be the maximum amount of on-chip memory for that device. The procedure to reconfigure the

amount of on-chip memory is as follows:

1) Jump to a location in program memory that will be unaffected by the change.

2) Disable interrupts by clearing the EA bit (

.7).

3) Write AAh to the Timed Access Register (

4) Write 55h to the Timed Access Register (

;C7h).

5) Modify the

Select bits (RMS[2:0]).

6) Delay 2 machine cycles (2 NOP instructions).

7) Enable interrupts by setting the EA bit (

If the 0kB of internal program memory setting is selected, extra precautions must be taken. In this case, it

will be necessary to duplicate the interrupt vector table in external program memory. This is because the

interrupt vector table is located in the lower 1kB of memory, and the device will automatically redirect

any fetches from the interrupt vector table to external memory. Care must be exercised when assembling

or compiling the program so that all the modules are located at the correct starting address, including the

interrupt vector table.

6.3 Program Memory Interconnect

shows the program memory interconnect scheme for the high-speed microcontroller family.

This example uses the DS80C320 and one 32kB x 8 EPROM. The program store enable (PSEN) signal is

used to provide an output enable to the EPROM. It can also be used to provide a chip enable, but this

produces less favorable timing. The address LSB and data are multiplexed on port 0, and the address

MSB is provided on port 2. An external latch, shown in the diagram as a 74F373, is used to latch the

lower byte of the address to the memory device. The Address Latch Enable (ALE) signal controls the

timing of the latch so that the operation is performed in the proper sequence. The signals and relative

timing for a program access are shown in

When implementing a high-speed memory interface, the F series (or faster) logic should be used. HC

logic will have worst-case propagation delays that are too long. Specifications for all devices should be

checked. More information on memory interface timing can be found in Application Note 57: DS80C320

Memory Interface Timing and Application Note 89: High-Speed Microcontroller Interface Timing.

The first product in the family, the DS80C320, provides an extremely high-speed interface to external

ROM or EPROM. This assures that the user can use the slowest, and least expensive, memory device for

a given crystal speed. The DS80C320 provides very fast slew rates, but controls ringing and overshoot.