2 serial port control 1 register (scon1; c0h), Serial port control 0 register (scon0; 98h) – Maxim Integrated High-Speed Microcontroller User Manual

Page 139

High-Speed Microcontroller User’s Guide

Rev: 062210

139 of 176

12.2.2

Serial Port Control 1 Register (SCON1; C0h)

Serial Port 1 performs identically to the standard Serial Port 0 on an 80C32 with one exception. The

baud-rate generation from Timer 2 is not available in Modes 1 and 3. Timer 1 is used. The port is located

at P1.3 and P1.2 for TXD1 and RXD1, respectively.

.7: Serial Port 1 Mode Bit 0 or Framing Error Flag (SM0/FE_1).

.6 (SMOD0)

determines whether this bit functions as SM0 or FE. The operation of SM0 (SMOD0 = 0) is described in

the table below. When SMOD0 = 1, the serial port will set FE to indicate an invalid stop bit. When used

as FE, this bit must be cleared in software.

.6: Serial Port 1 Mode Select 1 (SM1_1). The operation of SM1_1 is described in the table

below.

.5: Multiple MCU Communication (SM2_1). Setting this bit to a one enables multiprocessor

communication in Modes 2 or 3. If the ninth bit is 0, the RI_1 will not be set. In Mode 1, setting the

SM2_1 bit to a one causes the RI_1 bit not to be set if a valid stop bit is not received. In the high-speed

microcontroller, SM2_1 also has a new function. In mode 0, the SM2_1 bit controls whether the serial

port clock runs at a divide-by-4 or a divide-by-12 of the oscillator when not in PMM. When set to logic 0,

the serial port runs at a divide-by-12. When set to logic 1, the serial port runs at a divide-by-4. This

results in much faster synchronous serial communication.

.4: Receive Enable (REN_1). When set to 1, the receive shift register will be enabled.

.3: 9th Transmission Bit State (TB8_1). Set/clear to define the state of the ninth transmission

data bit in modes 2 and 3.

.2: 9th Received Bit State (RB8_1). Indicates the state of an incoming ninth bit when in modes 2

and 3. In mode 1, when SM2 = 0, RB8 is the state of the stop bit received. RB8 is not used in mode 0.

.1: Transmitter Interrupt Flag (TI_1). Flag that indicates the transmitted word has been

completely shifted out. In mode 0, TI is set at the end of the eighth data bit. In all other modes, this bit is

set at the end of the last data bit. It must be cleared manually by software.

.0: Receiver Interrupt Flag (RI_1). Flag that indicates a serial word has been received. In mode

0, RI_1 is set at the end of the eighth bit. In mode 1, it is set after the last sample of the incoming stop bit

subject to the state of SM2_1. In modes 2 and 3, RI_1 is set after the last sample of RB8_1. It must be

cleared manually by software.

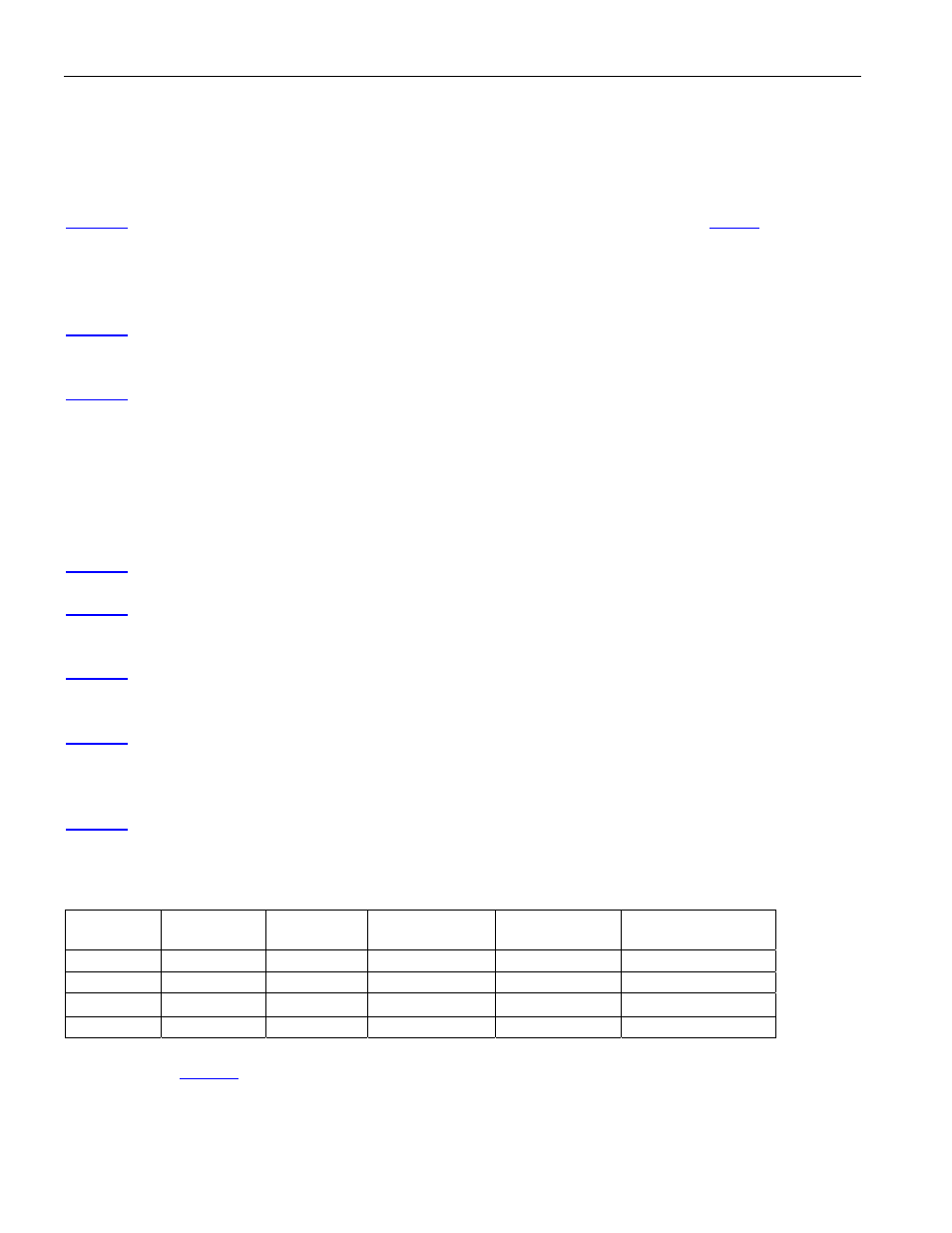

SM0/FE_0

SM1_0

MODE

FUNCTION

LENGTH

(BITS)

PERIOD

0 0 0 Sync 8

4/12

t

CLK

(see SM2)

0 1 1 Asynch 10 Timer

1

1 0 2 Asynch 11 64/32

t

CLK

1

1

3

Asynch

11

Timer 1

is set to 00h on a reset.

Read/Write Access: Unrestricted