Interrupts, 1 interrupt overview, Ystem – Maxim Integrated High-Speed Microcontroller User Manual

Page 105: Isable

High-Speed Microcontroller User’s Guide

Rev: 062210

105 of 176

9.

INTERRUPTS

The high-speed microcontroller family utilizes a three-priority interrupt system. The number of interrupts

varies according to the specific device. Each source has an independent priority bit, flag, interrupt vector,

and enable. In addition, interrupts can be globally enabled (or disabled). The system is compatible with

the original 8051 family. All of the original interrupts are available.

Several new sources have been added with new associated control and status bits, and new interrupt

vectors. Note that the interrupt vector table can extend from 0000h to 006Bh, so existing code may

require a relocation of the start address to avoid a conflict with the upper end of the vector table. A

summary of all interrupts appears in

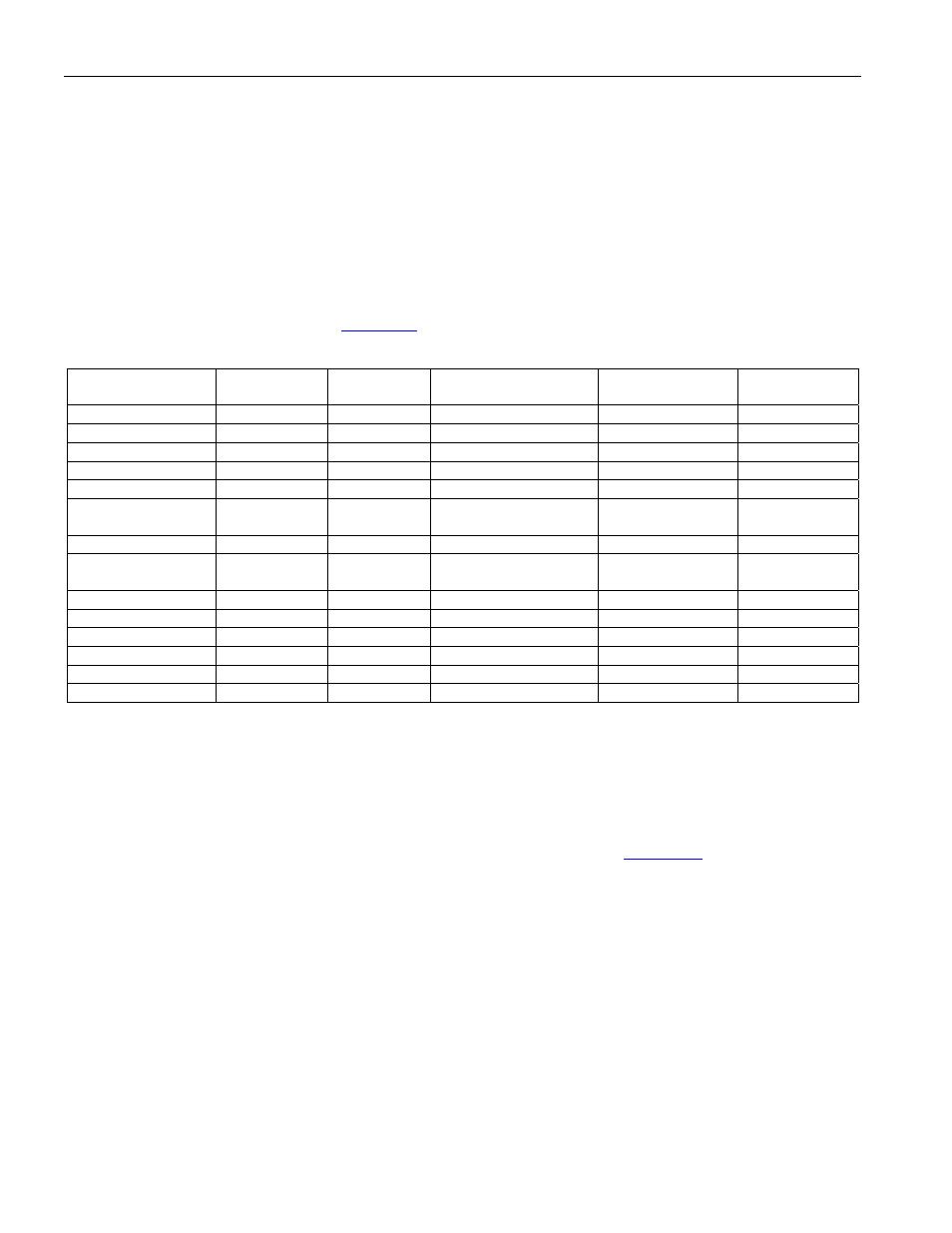

Table 9-A. Interrupt Summary

INTERRUPT

INTERRUPT

VECTOR

NATURAL

PRIORITY

FLAG ENABLE

PRIORITY

CONTROL

Power-Fail Indicator

33h

0

PFI (WDCON.4) EPFI

(WDCON.5)

N/A

External Interrupt 0

03h

1

IE0 (TCON.1)**

EX0 (IE.0)

PX0 (IP.0)

Timer 0 Overflow

0Bh

2

TF0 (TCON.5)*

ET0 (IE.1)

PT0 (IP.1)

External Interrupt 1

13h

3

IE1 (TCON.3)**

EX1 (IE.2)

PX1 (IP.2)

Timer 1 Overflow

1Bh

4

TF1 (TCON.7)*

ET1 (IE.3)

PT1 (IP.3)

Serial Port 0

23h

5

RI_0 (SCON0.0),

TI_0 (SCON0.1)

ES0 (IE.4)

PS0 (IP.4)

Timer 2 Overflow

2Bh

6

TF2 (T2CON.7)

ET2 (IE.5)

PT2 (IP.5)

Serial Port 1

3Bh

7

RI_1 (SCON1.0),

TI_1 (SCON1.1)

ES1 (IE.6)

PS1 (IP.6)

External Interrupt 2

43h

8

IE2 (EXIF.4)

EX2 (EIE.0)

PX2 (EIP.0)

External Interrupt 3

4Bh

9

IE3 (EXIF.5)

EX3 (EIE.1)

PX3 (EIP.1)

External Interrupt 4

53h

10

IE4 (EXIF.6)

EX4 (EIE.2)

PX4 (EIP.2)

External Interrupt 5

5Bh

11

IE5 (EXIF.7)

EX5 (EIE.3)

PX5 (EIP.3)

Watchdog Interrupt

63h

12

WDIF (WDCON.3)

EWDI (EIE.4)

PWDI (EIP.4)

Real-Time Clock

6Bh

13

RTCIF (RTCC.1)

ERTCI (EIE.5)

PRTCI (EIP.5)

Note: Unless marked, these flags must be cleared manually by software.

*Cleared automatically by hardware when the service routine is vectored to.

**If edge-triggered, cleared automatically by hardware when the service routine is vectored to. If level-triggered, flag follows the state of the pin.

9.1 Interrupt Overview

An interrupt allows the software to react to unscheduled or asynchronous events. When an interrupt

occurs, the CPU is expected to “service” the interrupt. This service takes the form of an interrupt service

routine (ISR). The ISR resides at a predetermined address as shown in

. When the interrupt

occurs, the CPU will vector to the appropriate location. It will run the code found at this location, staying

in an interrupt service state until done with the ISR. Once an ISR has begun, it can be interrupted only by

a higher priority interrupt. The ISR is terminated by a return from interrupt instruction (RETI). When an

RETI is performed, the processor will return to the instruction that would have been next when the

interrupt occurred.

Each interrupt source has an associated vector. This is the address to which the CPU will jump when the

interrupt occurs. When the interrupt condition occurs, the processor will also indicate this by setting a flag

bit. This bit is set regardless of whether the interrupt is enabled or not. That is, the flag responds to the

condition, not the interrupt. Most flags must be cleared manually by software. However, IE0 and IE1 are

cleared automatically by hardware when the service routine is vectored to if the interrupt was edge

triggered. In level-triggered mode, the flag follows the state of the pin. Flags TF0 and TF1 are always

cleared automatically when the service routine is vectored to. Refer to the individual bit descriptions for