1 crystal resume from stop mode, 3 ring oscillator wake-up from stop, Ower – Maxim Integrated High-Speed Microcontroller User Manual

Page 94: Onservation, Idle mode, Stop mode, Table 7-a, Shows the state of the processo

High-Speed Microcontroller User’s Guide

Rev: 062210

94 of 176

A second method of exiting Stop mode is with a reset. The watchdog timer reset is not available as a reset

source because no timers are running in Stop mode. An external reset via the RST pin will

unconditionally exit the device from Stop mode. If the BGS bit is set, the device will provide a reset

while in Stop mode if V

CC

should drop below the V

RST

level. If the BGS bit is 0, then a dip in power

below V

RST

will not cause a reset. For example, if V

CC

should drop to a level of V

RST

- 0.5V, then return

to the full level, no reset will be generated. For this reason, use of the bandgap reference is recommended

if a brownout condition is possible in Stop mode. If power-fails completely (V

CC

= 0V), then a power-on

reset will still be performed when V

CC

is reapplied regardless of the state of the BGS bit. Processor

operation will resume execution from address 0000h like any other reset.

7.2.2.1 Crystal Resume from Stop Mode

If the microcontroller does not contain a ring oscillator, or if the RGSL bit is 0, a device exiting Stop

mode must restart operation using the external crystal as a clock source. The device will experience a

power-on reset delay of 65,536 external clock cycles to allow the crystal to begin oscillation and the

frequency to stabilize. Once this delay is complete, software will begin execution from either address

0000h or the appropriate interrupt vector, depending on the stimulus to exit Stop mode. The same 65,536

external clock cycle delay is performed if an external crystal oscillator is used instead of an external

crystal.

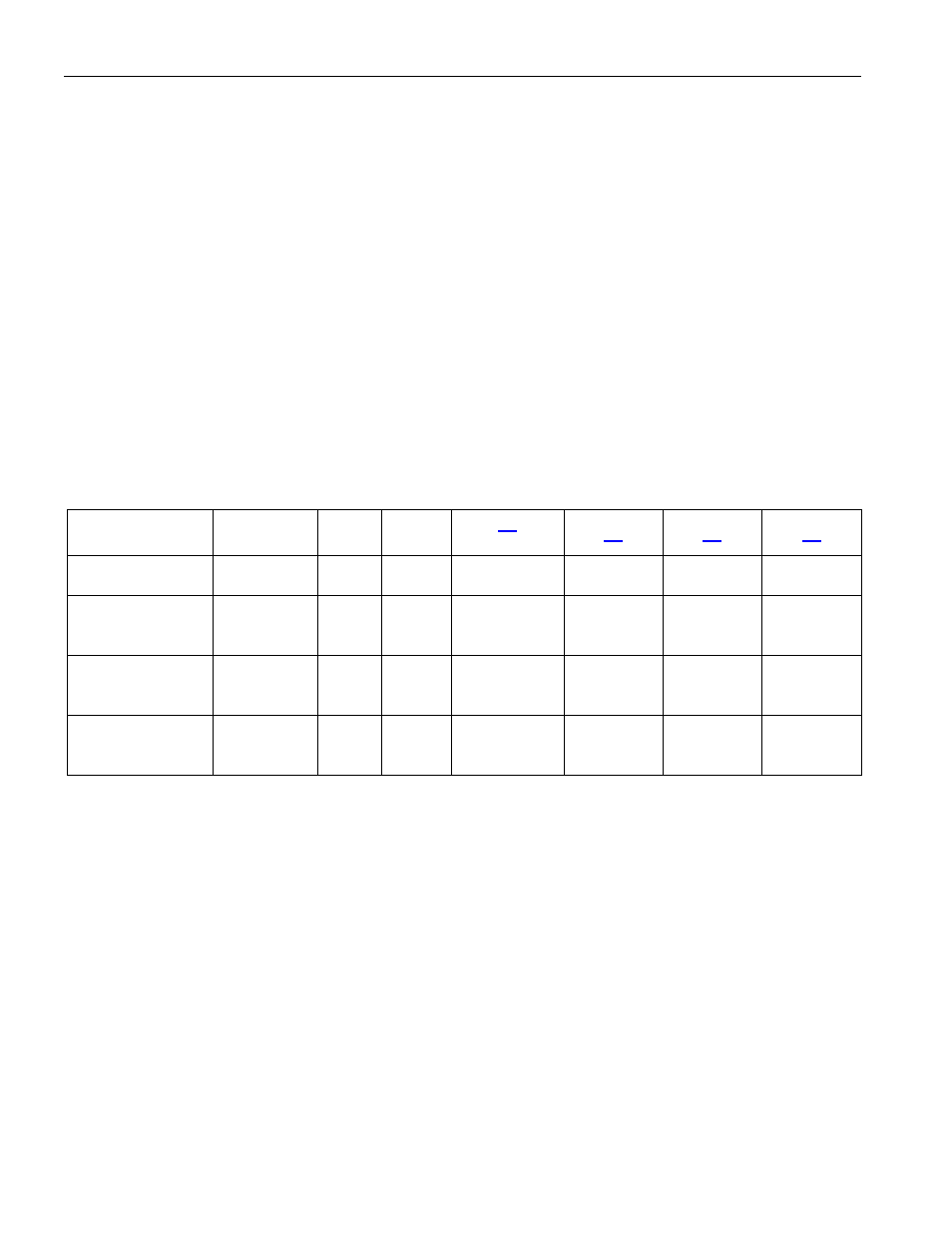

Table 7-A. Pin States in Power-Saving Modes

DEVICE

MODE

ALE

PSEN

(AD0–AD7)

DS80C310,

DS80C320

Idle or Stop

1

1

Latched

1

Port

data

2

Latched

3

Port

data

2

All Others

Internal Program

Execution

Idle or Stop

1

1

Port data

2

Port

data

2

Port

data

2

Port

data

2

All Others

External Program

Execution

Idle 1 1

Latched

1

Port

data

2

Latched

3

Port

data

2

All Others

External Program

Execution

Stop 1 1

Port

data

2

Port

data

2

Port

data

4

Port

data

2

Note 1:

Port exhibits op code following instruction that sets the STOP bit. Port 0 is operating in true bidirectional mode and will drive

both a logic 1 and a logic 0.

Note 2:

Port reflects data stored in corresponding port SFR. Port 0 functions as an open-drain output in this mode.

Note 3:

Port exhibits address MSB of op code following instruction that sets the STOP bit.

Note 4:

Port reflects data stored in corresponding port SFR. In this mode, the port uses weak pullups. If a bit in the P2 SFR is a 1, the

corresponding device pin will transition slowly to a high when the reset state is entered.

7.2.3 Ring Oscillator Wake-Up from Stop

A typical low-power application method is to keep the processor in Stop mode most of the time.

Periodically, the system will wake up (using an external interrupt), take a reading of some condition, then

return to sleep. The duration of full power operation is as short as possible. One disadvantage to this

method is that the clock must be restarted prior to performing a meaningful operation. This startup period

is a waste of time and power since no work can be performed. The high-speed microcontroller provides

an alternative.

If the Ring Select (RGSL) is enabled, the high-speed microcontroller can exit Stop mode running from an

internal Ring Oscillator. Upon receipt of an interrupt, this oscillator can start instantaneously, allowing

software execution to begin immediately while the oscillator is stabilizing. Once 65,536 clock cycles have

been detected, the CPU will automatically switch to the normal oscillator as its clock source. Some