5 data memory access, Figure 6-1. program memory interface, Figure 6-2. program memory signals – Maxim Integrated High-Speed Microcontroller User Manual

Page 81

High-Speed Microcontroller User’s Guide

Rev: 062210

81 of 176

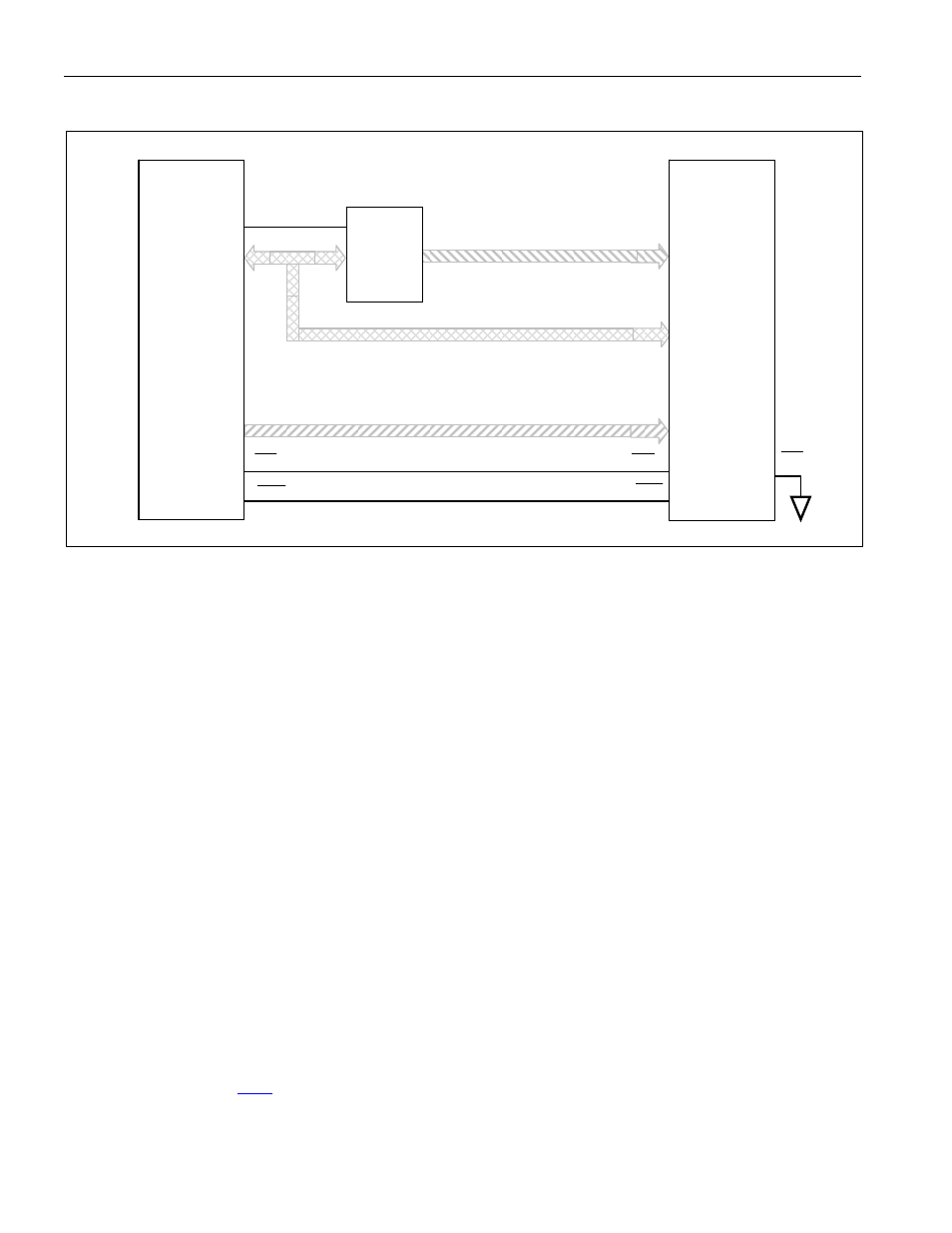

Figure 6-3. Data Memory Interface

6.5 Data Memory Access

As mentioned above, the high-speed microcontroller uses the MOVX instruction for data memory access.

This includes off-chip RAM and memory mapped peripherals needing read/write access. Several aspects

of the MOVX operation have been enhanced as compared to the original 8051. The principal

improvements are in the areas of the MOVX timing and the data pointer.

The MOVX instruction is used to generate read/write access to off-chip address locations. It has several

addressing modes. The first uses the MOVX @Ri command to reach a 256-byte block. This instruction

uses the value in the designated working register to address one of 256 locations. The upper byte of the

address is supplied by the value in the Port 2 latch. A second way to access data is the Data Pointer

(DPTR). This 16-bit register provides an absolute address for data memory access; 16-bits cover the

entire 64kB area, thus the DPTR serves as a pointer to memory. Using the DPTR, the relevant instruction

is MOVX @DPTR.

The original 8051 contained one DPTR. While this provides access to the entire memory area, it is

difficult to move data from one address to another. The high-speed microcontroller provides two data

pointers. Thus software can load both a source and a destination address. The MOVX instruction will use

the active pointer to direct the off-chip address.

The data pointers are called DPTR0 and DPTR1. DPTR0 is located at SFR addresses 82h and 83h. These

are the locations used by the original 8051. No modification of standard code is needed to use DPTR0.

The new DPTR is located at SFR 84h and 85h. The Data Pointer Select bit (SEL) chooses the active

pointer and is located at the LSb of the SFR location 86h. No other bits in register 86h have any effect

and are set to 0. When

is set to 0, the DPTR0 is active. When set to 1, DPTR1 is used.

RD

(P3.7)

ALE

LBS ADDRESS

OE

DATA BUS

MSB ADDRESS

(8)

(5)

8kB X 8

SRAM

(8)

CE

WR

(P3.6)

WE

DS80C320

74F373

LATCH