1 romsize feature, Memory access, Nternal – Maxim Integrated High-Speed Microcontroller User Manual

Page 77: Rogram, Emory

High-Speed Microcontroller User’s Guide

Rev: 062210

77 of 176

Another advantage of internal data memory is that it guarantees a two-machine cycle data memory

access. This data can be made nonvolatile on the DS87C530 through the use of an external battery.

Restricting memory operations within the on–chip memory allows ports 0 and 2 to be used for general

purpose I/O. For more information concerning memory size for a specific device, consult the

corresponding data sheet.

Upon a power-on reset, the internal data memory area is disabled and transparent to the system map. Any

memory access between 0000h and FFFFh will be directed to the Expanded bus. This allows the device to

remain drop-in compatible with existing 87C52 designs. To enable the internal SRAM area, software

must configure the Data Memory Enable bits DME1, DME0 (

.1-0). The three memory

configurations shown in

are supported to allow either external data memory access via the

expanded bus, internal data memory access, or read-only access to the EPROM System Control Byte.

Note that these bits are cleared after a reset, so access to the internal data memory is prohibited until these

bits are modified. The contents of internal data memory are not affected by the changing of the Data

Memory Enable bits.

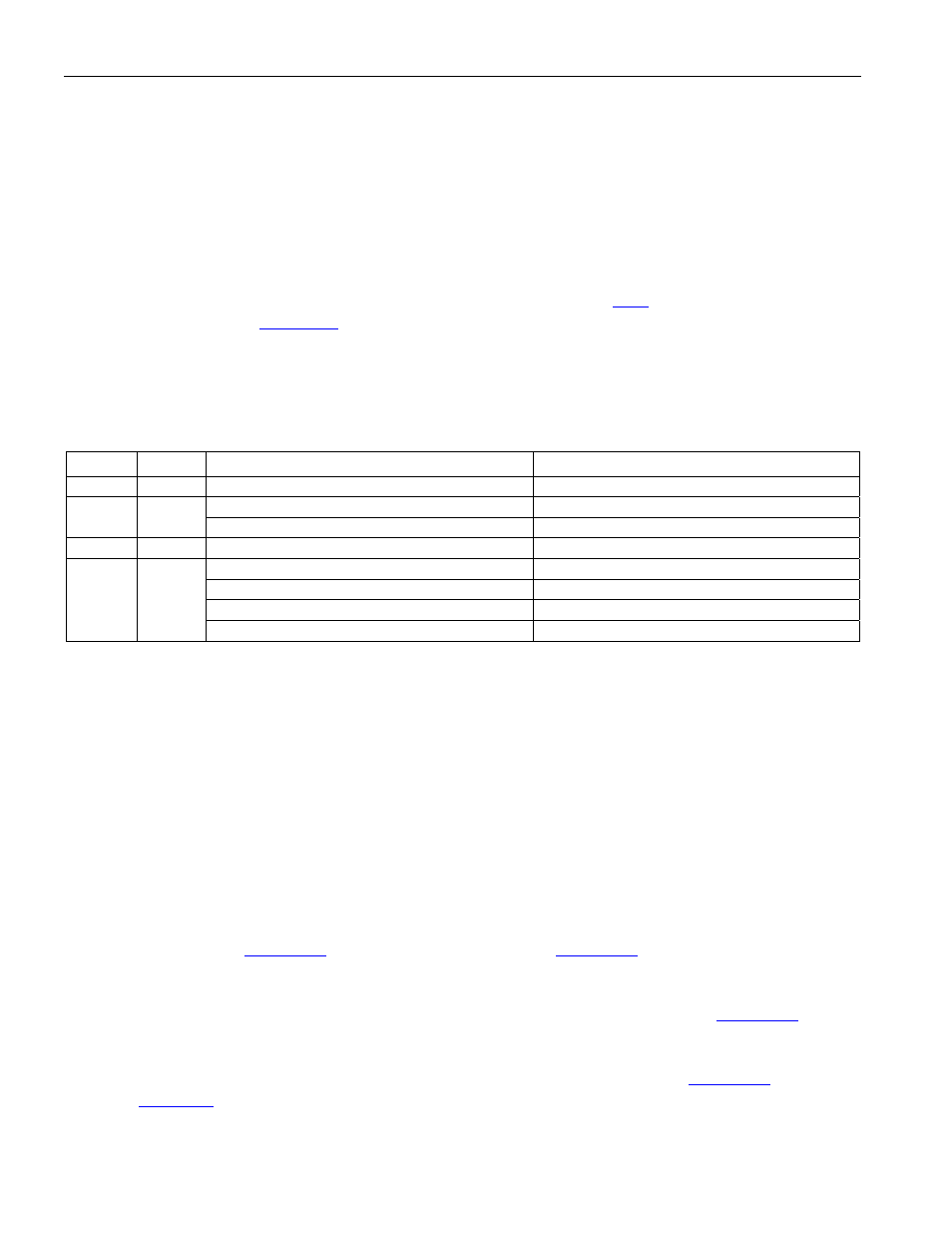

Table 6-A. Data Memory Access Control

DME1

DME0

DATA MEMORY ADDRESS RANGE

DATA MEMORY LOCATION

0

0

0000h–FFFFh

External Data Memory (default)

0000h–03FFh Internal

Data

Memory

0 1

0400h–FFFFh

External Data Memory

1 0

Reserved

Reserved

0000h–03FFh Internal

Data

Memory

0400h–FFFBh Reserved

FFFCh

System Control Byte (Read only)

1 1

FFFDh–FFFFh Reserved

6.2.1 ROMSIZE Feature

Members of the high-speed microcontroller family that incorporate internal program memory allow the

system to dynamically vary the on-chip memory size. This permits the device to reconfigure the upper

limit of on-chip memory, allowing a portion of the memory to be mapped off-chip. The size of on-chip

memory can vary from 0kB to the full range of memory, allowing the device to behave like a device with

less on-chip memory.

This feature has two primary uses. In the first instance, it allows the device to act as a bootstrap loader for

a flash memory or nonvolatile SRAM (NV SRAM). The internal program memory can contain a

bootstrap loader, which can program the external memory device. Secondly, this method can be used to

increase the amount of available program memory from 64kB to 80kB without bank switching.

The maximum amount of on-chip memory is selected by configuring the ROM Size Select register bits

RMS2, RMS1, RMS0 (

.2-0). The modification of the

register must be followed by

a two-machine cycle delay, such as executing two NOP instructions, before jumping to the new address

range. Interrupts must be disabled during this operation, because a jump to the interrupt vector during the

changing of the memory map can cause erratic results. In addition, modification of the

register

must be done from a location that will be valid both before and after the on-chip memory configuration. If

off-chip memory access is planned, it is recommended that ports 0 and 2 not be used as general purpose

I/O, as their state will be disturbed by the memory operations. The settings for the

. Note that the memory configurations shown are not available on all devices.