56 real-time clock day register 0 (rtcd0), 57 real-time clock day register 1 (rtcd1), 3 instruction timing – Maxim Integrated High-Speed Microcontroller User Manual

Page 58: Real-time clock second register (rtcs), Real-time clock minute register (rtcm), Real-time clock hour register (rtch), Rtcd0, Rtcd1, Ffh) are ignored. attem

High-Speed Microcontroller User’s Guide

Rev: 062210

58 of 176

4.2.56

Real-Time Clock Day Register 0 (RTCD0)

7 6 5 4 3 2 1 0

SFR FEh RTCD0.7

RTCD0.6 RTCD0.5 RTCD0.4 RTCD0.3 RTCD0.2 RTCD0.1 RTCD0.0

R*W*-*

R*W*-*

R*W*-*

R*W*-*

R*W*-*

R*W*-*

R*W*-* R*W*-*

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset, * = See Description

RTCD0.7–RTCD.0

Bits 7-0

Real-Time Clock Day Register 0. This register contains the least significant byte of the

16-bit current day count. This is not an absolute value tied to a specific calendar date,

but rather a relative day count defined by the user. This register can be read only when

the RTCRE bit is set, and can only be modified when the RTCWE bit is set. Consult the

description of the RTCWE bit for the programming protocol for this register. The

register counts from 0h to FFh. No alarm corresponds to these bits.

4.2.57

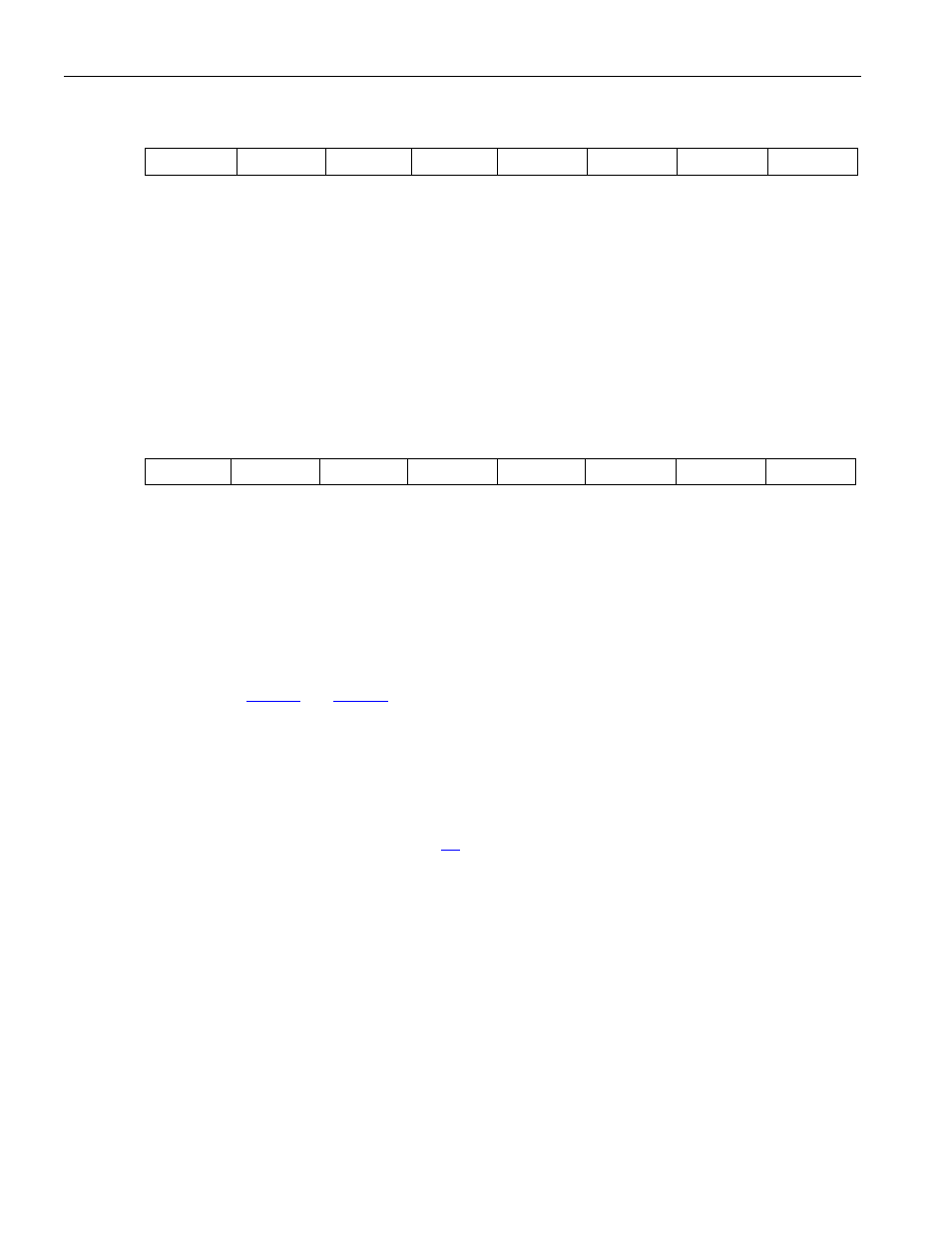

Real-Time Clock Day Register 1 (RTCD1)

7 6 5 4 3 2 1 0

SFR FFh RTCD1.7 RTCD1.6 RTCD1.5 RTCD1.4 RTCD1.3 RTCD1.2 RTCD1.1 RTCD1.0

R*W*-*

R*W*-*

R*W*-*

R*W*-*

R*W*-* R*W*-* R*W*-* R*W*-*

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset, * = See Description

RTCD1.7–RTCD1.0

Bits 7–0

Real-Time Clock Day Register 1. This register contains the most significant byte of

the 16-bit current day count. This is not an absolute value tied to a specific calendar

date, but rather a relative day count defined by the user. This register can be read only

when the RTCRE bit is set, and can only be modified when the RTCWE bit is set.

Consult the description of the RTCWE bit for the programming protocol for this

register. The register counts from 0h to FFh. A rollover of this register will clear

. No alarm corresponds to these bits.

4.3 Instruction Timing

All instructions in the high-speed microcontroller perform the same functions as their 80C32

counterparts. Their affect on bits, flags, and other status functions is identical. However, the timing of

each instruction is different. This applies both in absolute terms of nanoseconds for a given crystal, and in

relative terms of clocks. For absolute timing of real-time events, the timing of software loops will need to

be calculated using the data provided in Section

: Instruction Set Details. However, timers default to

run at the older 12 clocks per timer increment and timer-based events need no modification.

The relative time of two instructions might be different in the new architecture than it was previously. For

example, both the one-byte, two-cycle “MOVX A, @DPTR” instruction and the three-byte, two-cycle

“MOV direct, direct” instruction used two cycles. In the high-speed microcontroller, the MOVX

instruction uses two cycles but the “MOV direct, direct” uses three cycles. While both are faster than their

original counterparts, they now have different execution times from each other because the high-speed

microcontroller typically uses one cycle for each byte. This is generally true for all instructions except for

MUL, DIV, MOVC, MOVX, and branch type instructions. The timing of each instruction should be

examined for familiarity with the changes. Note that a machine cycle now requires just four clocks, and

provides one ALE pulse per cycle. Many instructions require only one cycle, but some require five. In the

original architecture, all were one or two cycles except for MUL and DIV.