17 external interrupt flag (exif), Port 1 (p1), Exif – Maxim Integrated High-Speed Microcontroller User Manual

Page 33

High-Speed Microcontroller User’s Guide

Rev: 062210

33 of 176

4.2.17

External Interrupt Flag (EXIF)

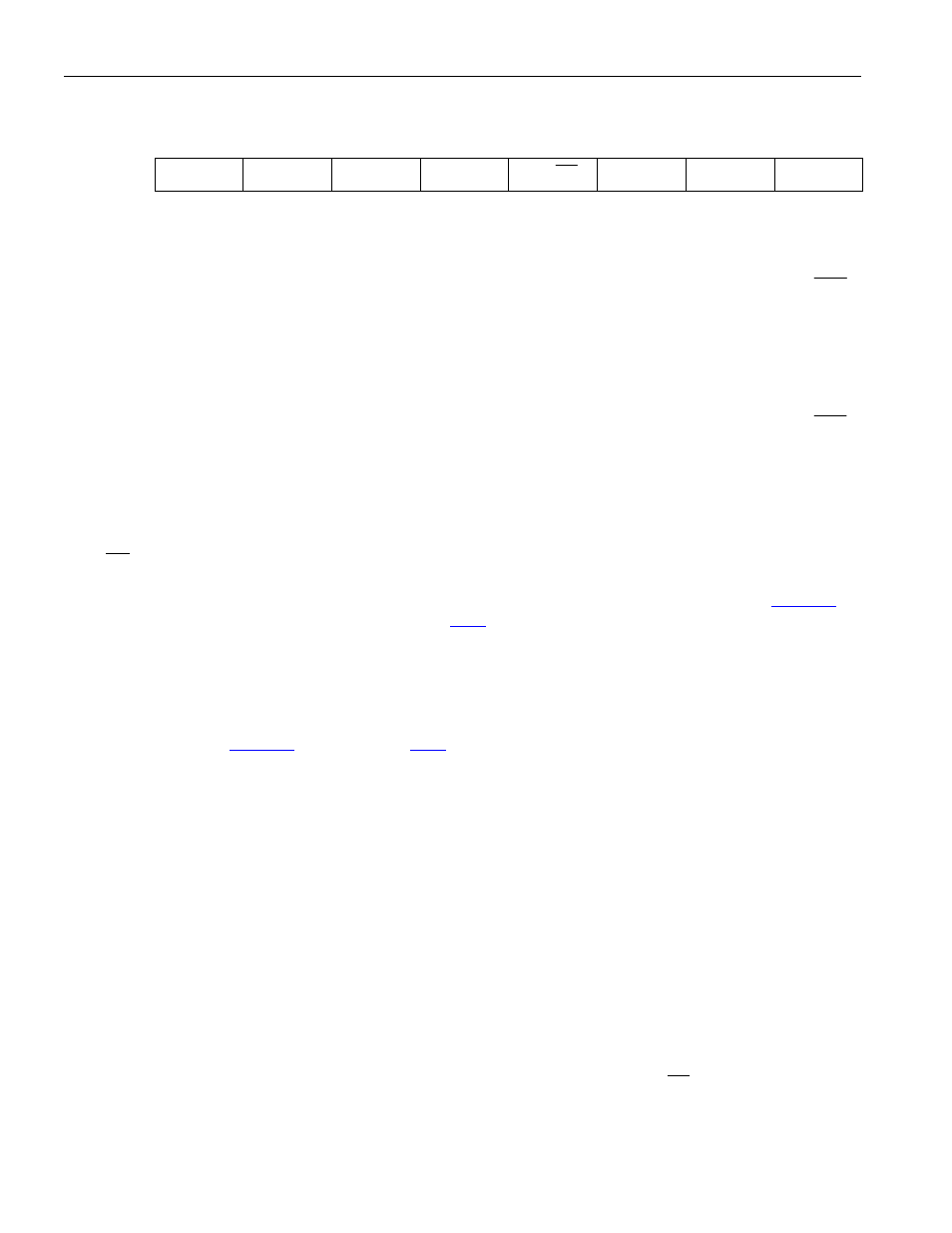

7 6 5 4 3 2 1 0

SFR 91h

IE5 IE4 IE3

IE2

XT/

RG

RGMD

RGSL BGS

RW-0 RW-0 RW-0 RW-0 RW-* R-*

RW-* RT-0

R = Unrestricted Read, W = Unrestricted Write, T = Timed Access Write Only-n = Value after Reset, * = See description

IE5

Bit 7

External Interrupt 5 Flag. This bit will be set when a falling edge is detected on

INT5

.

This bit must be cleared manually by software. Setting this bit in software will cause an

interrupt if enabled.

IE4

Bit 6

External Interrupt 4 Flag. This bit will be set when a rising edge is detected on INT4.

This bit must be cleared manually by software. Setting this bit in software will cause an

interrupt if enabled.

IE3

Bit 5

External Interrupt 3 Flag. This bit will be set when a falling edge is detected on

INT3

.

This bit must be cleared manually by software. Setting this bit in software will cause an

interrupt if enabled.

IE2

Bit 4

External Interrupt 2 Flag. This bit will be set when a rising edge is detected on INT2.

This bit must be cleared manually by software. Setting this bit in software will cause an

interrupt if enabled.

XT/

RG

Bit 3

Crystal/Ring Source Select. This bit selects the crystal oscillator or ring oscillator as the

desired clock source. This bit will be the inverse of RGMD except during the crystal

warmup period when executing a ring oscillator resume from Stop. XTUP (

must be set to 1 and XTOFF (

.3) must be cleared to 0 before this bit can be set.

Attempts to modify this bit when these conditions are not met will be ignored. This bit must

be cleared before XTOFF can be set to 1. This bit is set to 1 after a power-on reset, and

unchanged by all other forms of reset. This bit is not used on the DS80C310 or DS80C320

and will be 1 when read.

0 = The ring oscillator is selected as the clock source. This setting is unaffected by XTUP

(

.3).

1 = The crystal oscillator is selected as the clock source. This setting is invalid unless

XTUP = 1 and XTOFF = 0.

RGMD

Bit 2

Ring Mode Status. This bit indicates the current clock source for the device. This bit

is cleared to 0 after a power-on reset, and unchanged by all other forms of reset. The

state of this bit will be undefined on devices that do not incorporate a ring oscillator.

0 = Device is operating from the external crystal or oscillator.

1 = Device is operating from the ring oscillator.

RGSL

Bit 1

Ring Oscillator Select. This bit selects the clock source following a resume from Stop

mode. Using the ring oscillator to resume from Stop mode allows almost instantaneous

startup. This bit is cleared to 0 after a power-on reset, and unchanged by all other forms of

reset. The state of this bit will be undefined on devices that do not incorporate a ring

oscillator.

0 = The device will hold operation until the crystal oscillator has warmed up.

1 = The device will begin operating from the ring oscillator, and when the crystal warmup

is complete, will switch to the clock source indicated by the XT/

RG

bit.