10 timer mode control (tmod), Timer/counter control (tcon), Tmod – Maxim Integrated High-Speed Microcontroller User Manual

Page 29

High-Speed Microcontroller User’s Guide

Rev: 062210

29 of 176

4.2.10

Timer Mode Control (TMOD)

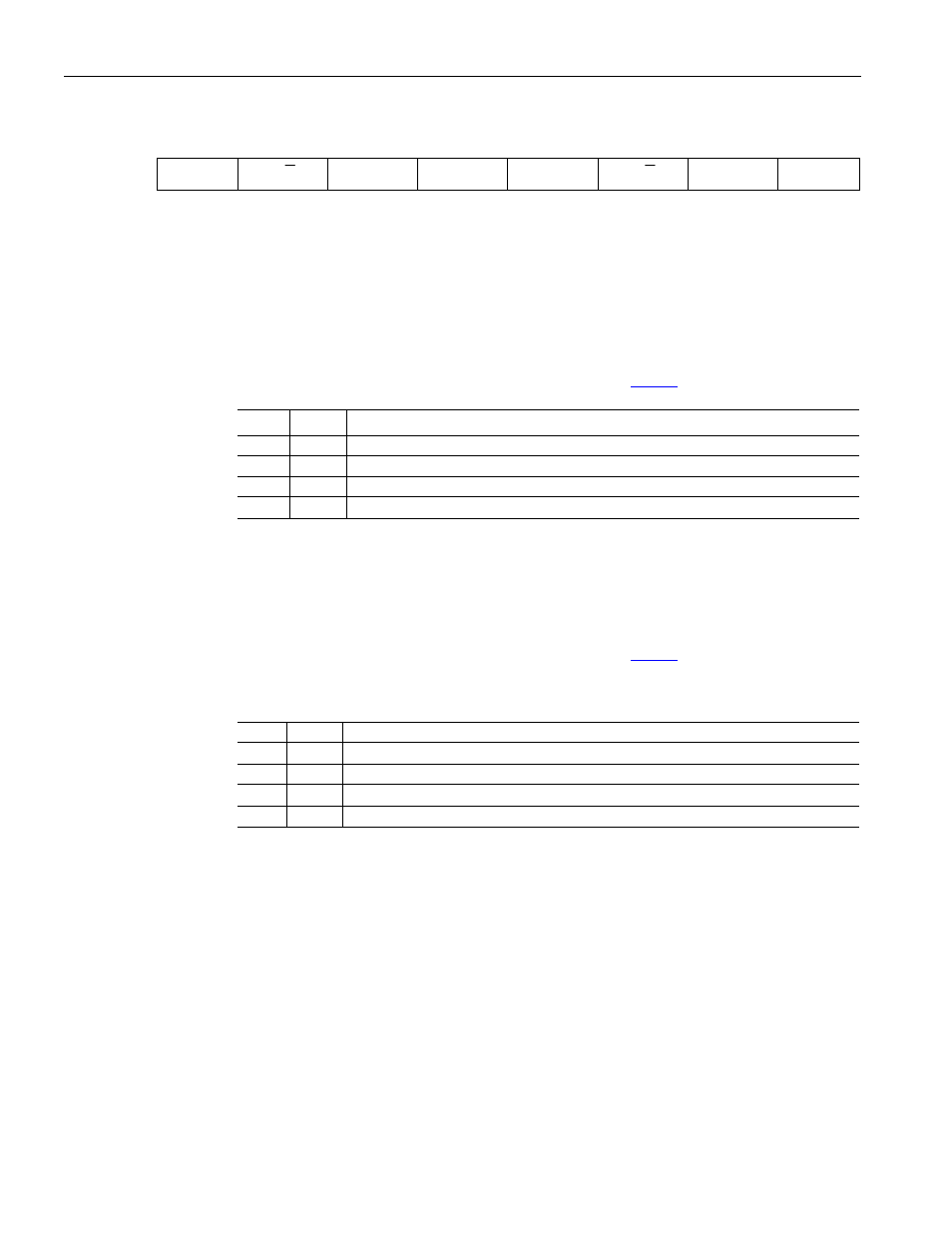

7 6 5 4 3 2 1 0

SFR 89h

GATE

C/

T

M1

M0 GATE C/ T

M1 M0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

GATE

Bit 7

Timer 1 Gate Control. This bit enable/disables the ability of Timer 1 to increment.

0 = Timer 1 will clock when TR1 = 1, regardless of the state of

INT1.

1 = Timer 1 will clock only when TR1 = 1 and

INT1 = 1.

C/

T

Bit 6

Timer 1 Counter/Timer Select.

0 = Timer 1 is incremented by internal clocks.

1 = Timer 1 is incremented by pulses on T1 when TR1 (

.6) is 1.

Timer 1 Mode Select. These bits select the operating mode of Timer 1.

M1 M0 Mode

0

0

Mode 0: 8 bits with 5-bit prescale

0

1

Mode 1: 16 bits

1

0

Mode 2: 8 bits with auto-reload

1

1

Mode 3: Timer 1 is halted, but holds its count

M1, M0

Bits 5, 4

GATE

Bit 3

Timer 0 Gate Control. This bit enables/disables that ability of Timer 0 to increment.

0 = Timer 0 will clock when TR0 = 1, regardless of the state of

INT0.

1 = Timer 0 will clock only when TR0 = 1 and

INT0 = 1.

C/

T

Bit 2

Timer 0 Counter/Timer Select.

0 = Timer 0 incremented by internal clocks.

1 = Timer 0 is incremented by pulses on T0 when TR0 (

.4) is 1.

Timer 0 Mode Select. These bits select the operating mode of Timer 0. When Timer 0

is in mode 3, TL0 is started/stopped by TR0 and TH0 is started/stopped by TR1. Run

control from Timer 1 is then provided via the Timer 1 mode selection.

M1 M0

Mode

0

0

Mode 0: 8 bits with 5-bit prescale

0

1

Mode 1: 16 bits

1

0

Mode 2: 8 bits with auto-reload

1

1

Mode 3: Timer 0 is two 8-bit counters.

M1, M0

Bits 1, 0