1 speed reduction, 3 power management modes, Ring oscillator wake-up from stop – Maxim Integrated High-Speed Microcontroller User Manual

Page 95: Table 7-a. pin states in power-saving modes

High-Speed Microcontroller User’s Guide

Rev: 062210

95 of 176

devices incorporate the option of continuing to run from the ring oscillator following Stop mode even

after the 65,536 clock cycle period. However, if the required interrupt response is very short, the software

can re-enter Stop mode before the crystal is even stable. In this case, Stop mode can be invoked and both

oscillators will be stopped.

7.2.3.1 Speed Reduction

The high-speed microcontroller is a fully CMOS 8051-compatible microcontroller. It can use

significantly less power than other 8051 versions because it is more efficient. As an average, software

will run 2.5 times faster on the high-speed microcontroller than on other 8051 derivatives. The same job

can be accomplished by slowing down the crystal by a factor of 2.5. For example, an existing 8051 design

that runs at 12MHz can run at approximately 4.8MHz on the high-speed microcontroller. At this reduced

speed, the high-speed microcontroller will have lower power consumption than an 8051, yet perform the

same job.

Using the 2.5x factor,

shows the approximate speed at which the high-speed microcontroller

can accomplish the same work as an 8051. The exact improvement will vary depending on the actual

instruction mix. Available crystal speeds must also be considered. See Section

for information on

instruction timing.

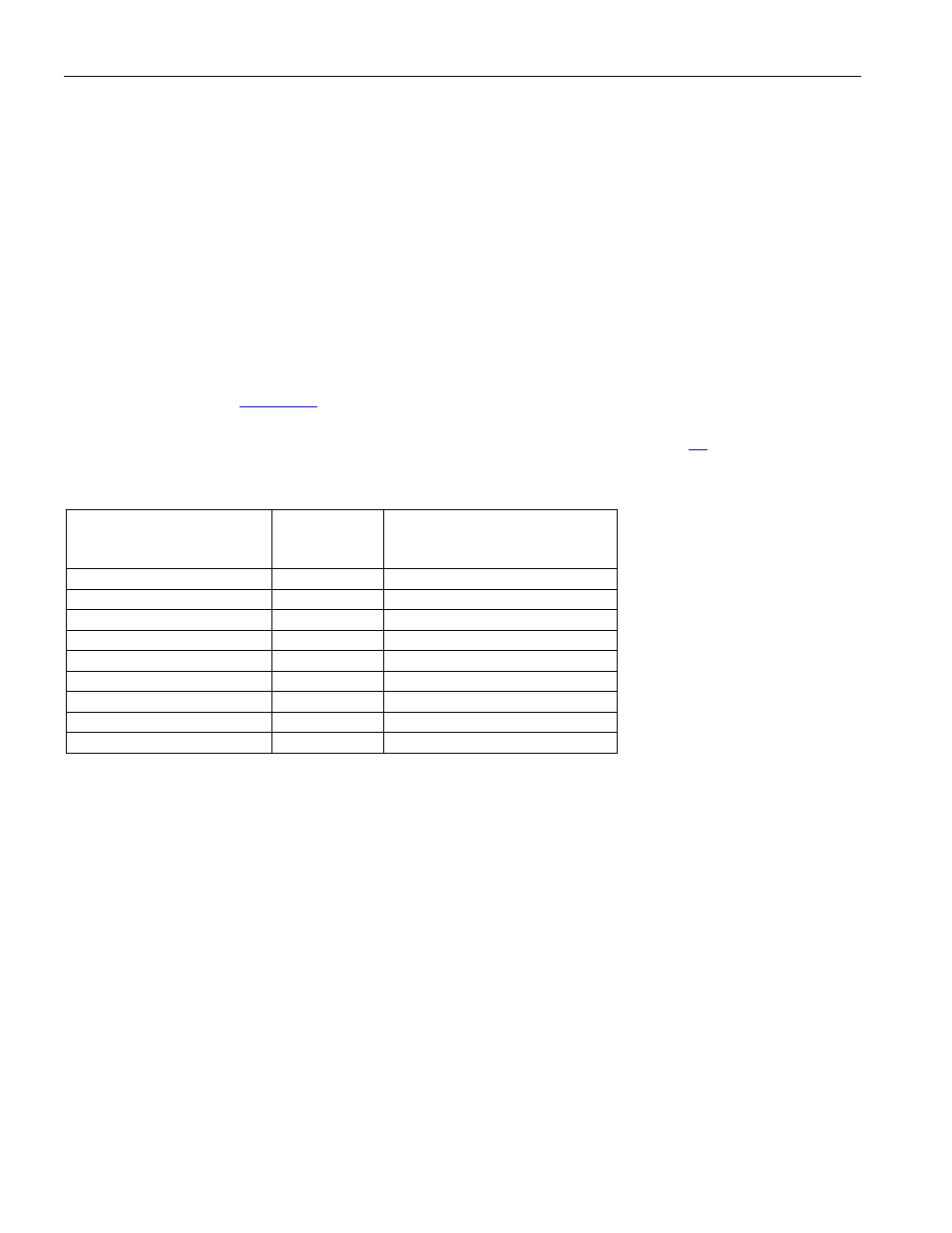

Table 7-B. Crystal vs. MIPS Comparison

ORIGINAL 8051

CRYSTAL SPEED

(MHz)

MIPS

HIGH-SPEED

MICROCONTROLLER

CRYSTAL SPEED (MHz)

3.57

0.3 1.4

7.37

0.6 2.0

11.0592

0.9 4.4

14.318

1.2 5.7

16

1.3 6.4

20

1.6 8.0

24 2.0 9.6

33

2.7 13.2

40

3.3 16

7.3 Power Management Modes

Power consumption in CMOS microcontrollers is a function of operating frequency. The Power

Management Mode (PMM) feature, available with some members of the high-speed microcontroller

family, allows software to dynamically match operating frequency and current consumption with the need

for processing power. Instead of the default 4 clocks per machine cycle, power management mode 1

(PMM1) and power management mode 2 (PMM2) utilize 64 and 1024 clocks per cycle respectively to

conserve power.

A number of special features have been added to enhance the function of the power management modes.

The switchback feature allows the device to almost instantaneously return to divide-by-4 mode upon

acknowledgment of an external interrupt or a falling edge on a serial port receiver pin. The advantages of

this become apparent when one calculates the increased interrupt service time of a device operating in

PMM. In addition, a device operating in PMM would normally be unable to sample an incoming serial

transmission to properly receive it. The switchback feature, explained below, allows a device to return to

divide-by-4 operation in time to receive incoming serial port data and process interrupts with no loss in

performance.