51 real-time clock control register (rtcc), Extended interrupt priority (eip), Rtcc – Maxim Integrated High-Speed Microcontroller User Manual

Page 55: 7). the contents of this register, 5). this register should

High-Speed Microcontroller User’s Guide

Rev: 062210

55 of 176

4.2.51

Real-Time Clock Control Register (RTCC)

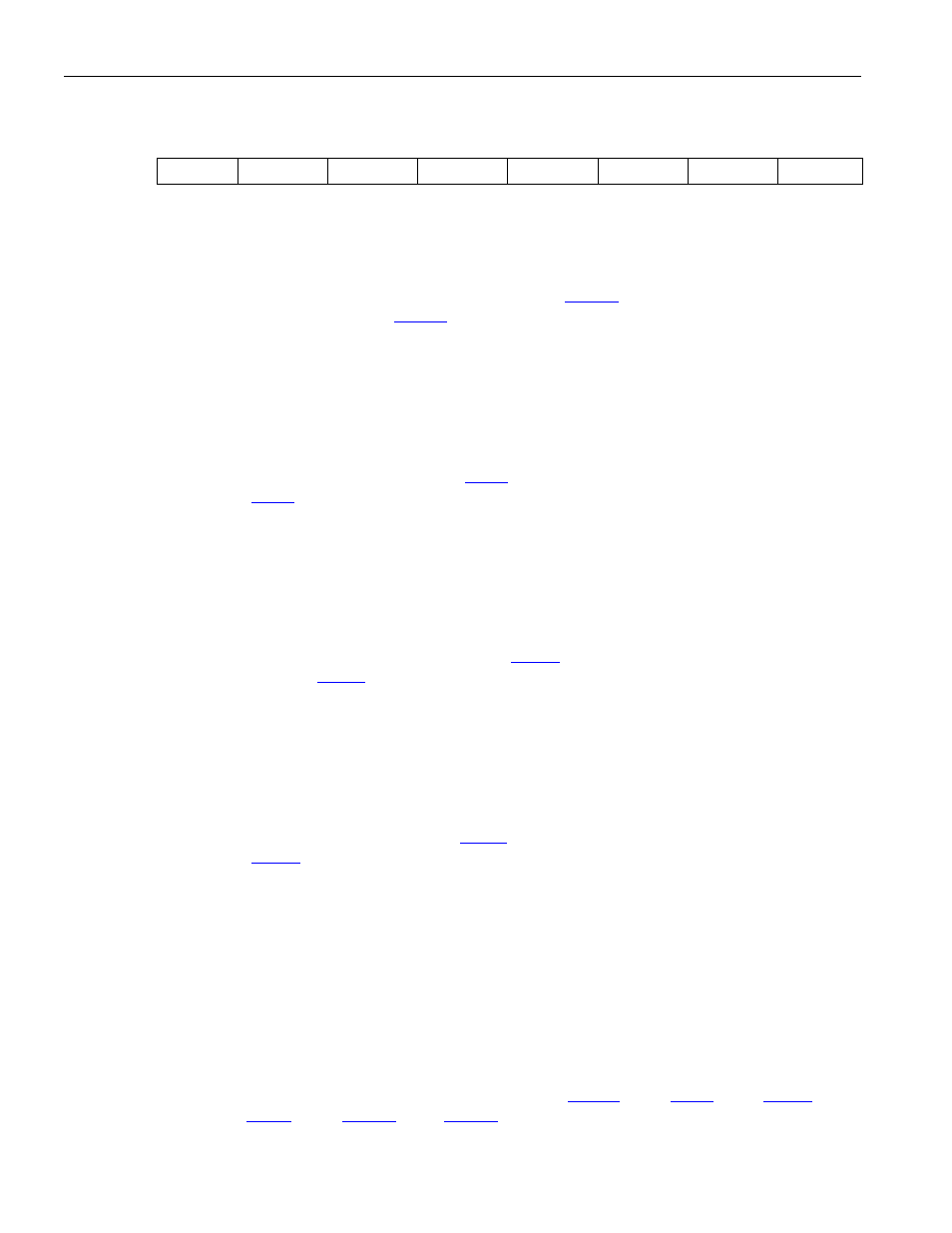

7 6 5 4 3 2 1 0

SFR F9h

SSCE

SCE

MCE

HCE RTCRE

RTCWE

RTCIF RTCE

RW-*

RW-* RW-* RW-* RW*-0 RT*-0 R*-* RT-*

R = Unrestricted Read, W = Unrestricted Write, T = Timed Access Write Only, -n = Value after Reset, * = See Description

SSCE

Bit 7

RTC Subsecond Register Compare Enable. This bit enables a match Bit 7 between

the Real-Time Alarm Subsecond Register (

;F2h) and the Real-Time Clock

Subsecond Register (

;FAh) to contribute to the RTC interrupt request. This bit

will be indeterminate following a no-battery reset, and is unaffected by all other resets.

0 = The subsecond value is a don’t care when evaluating the RTC alarm. If any other

alarm register compare bits are enabled, this will cause one interrupt per subsecond tick

(1/256 second) for as long as the other registers match.

1 = Include the subseconds along with any other registers when evaluating alarm

compare conditions.

SCE

Bit 6

RTC Second Register Compare Enable. This bit enables a match between the Real-

Time Alarm Second Register (

;F3h) and the Real-Time Clock Second Register

;FBh) to contribute to the RTC interrupt request. This bit will be indeterminate

following a no-battery reset, and is unaffected by all other resets.

0 = The second value is a don’t care when evaluating an RTC alarm. If any other alarm

register compare bits are enabled, this will cause one interrupt per second as long as the

other registers match.

1 = Include the second along with any other registers when evaluating alarm compare

conditions.

MCE

Bit 5

RTC Minute Register Compare Enable. This bit enables a match between Bit 5 the

Real-Time Alarm Minute Register (

;F4h) and the Real-Time Clock Minute

Register (

;FCh) to contribute to the RTC interrupt request. This bit will be

indeterminate following a no-battery reset, and is unaffected by all other resets.

0 = The minute value is a don’t care when evaluating an RTC alarm. If any other alarm

register compare bits are enabled, this will cause one interrupt per minute as long as the

other registers match.

1 = Include the minute along with any other registers when evaluating alarm compare

conditions.

HCE

Bit 4

RTC Hour Register Compare Enable. This bit enables a match between the Real-

Time Alarm Hour Register (

;F5h) and the Real-Time Clock Hour Register

;FDh) to contribute to the RTC interrupt request. This bit will be indeterminate

following a no-battery reset, and is unaffected by all other resets.

0 = The hour value is a don’t care when evaluating an RTC alarm. If any other alarm

register compare bits are enabled, this will cause one interrupt per hour for as long as

the other registers match.

1 = Include the hour along with any other registers when evaluating alarm compare

conditions.

RTCRE

Bit 3

RTC Read Enable. This bit temporarily halts internal updating of the RTC to allow

software to read the current time. No loss of time will occur. This bit will be cleared to

0 following any reset. Attempts to set the RTCRE and RTCWE bits simultaneously will

be ignored. When this bit is cleared, software must wait 4 machine cycles before setting

either the RTCRE or RTCWE bit again.

0 = Reads of the RTC clock registers (

;FAh,

;FBh,

;FCh,

;FDh,

;FFh) are prohibited and will return erroneous

values.