Table 4-d. ds80c320/ds80c323 sfr reset values – Maxim Integrated High-Speed Microcontroller User Manual

Page 21

High-Speed Microcontroller User’s Guide

Rev: 062210

21 of 176

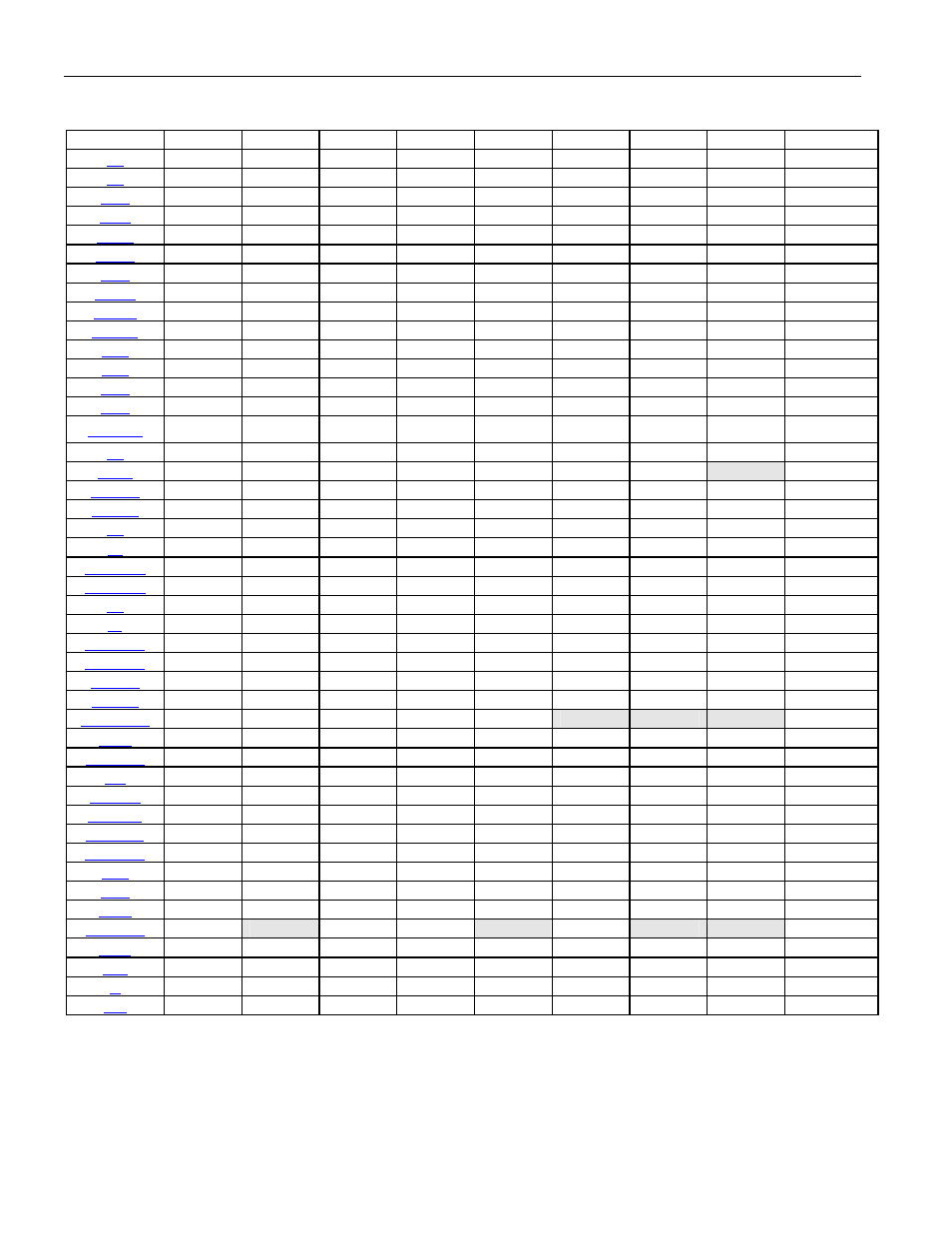

Table 4-E. DS83C520/DS87C520 SFR Locations

REGISTER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

ADDRESS

P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 80h

SP.7 SP.6 SP.5 SP.4 SP.3 SP.2 SP.1 SP.0 81h

DPL.7 DPL.6 DPL.5 DPL.4 DPL.3 DPL.2 DPL.1 DPL.0 82h

DPH.7 DPH.6 DPH.5 DPH.4 DPH.3 DPH.2 DPH.1 DPH.0

83h

DPL1.7 DPL1.6 DPL1.5 DPL1.4 DPL1.3 DPL1.2 DPL1.1 DL1H.0

84h

DPH1.7 DPH1.6 DPH1.5 DPH1.4 DPH1.3 DPH1.2 DPH1.1 DPH1.0

85h

SEL

86h

SMOD_0

SMOD0

— — GF1 GF0

STOP

IDLE 87h

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 88h

GATE C/

T

M1 M0

GATE

C/

T

M1 M0 89h

TL0.6

TL0.5 TL0.4 TL0.3 TL0.2 TL0.1 TL0.0 8Ah

TL1.6

TL1.5 TL1.4 TL1.3 TL1.2 TL1.1 TL1.0 8Bh

TH0.7 TH0.6 TH0.5 TH0.4 TH0.3 TH0.2 TH0.1 TH0.0 8Ch

TH1.7 TH1.6 TH1.5 TH1.4 TH1.3 TH1.2 TH1.1 TH1.0 8Dh

WD1 WD0 T2M T1M T0M MD2 MD1 MD0 8Eh

P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0 90h

XT/

RG

RGMD RGSL BGS 91h

SM0/FE_0

SM1_0 SM2_0 REN_0 TB8_0 RB8_0 TI_0 RI_0

98h

SBUF0.7 SBUF0.6 SBUF0.5 SBUF0.4 SBUF0.3 SBUF0.2 SBUF0.1 SBUF0.0

99h

P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 A0h

EA ES1 ET2 ES0 ET1 EX1 ET0 EX0 A8h

SADDR0.6

SADDR0.5 SADDR0.4 SADDR0.3 SADDR0.2 SADDR0.1 SADDR0.0

A9h

SADDR1.6

SADDR1.5 SADDR1.4 SADDR1.3 SADDR1.2 SADDR1.1 SADDR1.0

AAh

P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0 B0h

— PS1 PT2 PS0 PT1 PX1 PT0 PX0 B8h

SADEN0.7 SADEN0.6 SADEN0.5 SADEN0.4 SADEN0.3 SADEN0.2 SADEN0.1 SADEN0.0

B9h

SADEN1.7 SADEN1.6 SADEN1.5 SADEN1.4 SADEN1.3 SADEN1.2 SADEN1.1

SADEN1.0

BAh

SM0/FE_1 SM1_1 SM2_1 REN_1 TB8_1 RB8_1 TI_1 RI_1

C0h

SBUF1.7 SBUF1.6 SBUF1.5 SBUF1.4 SBUF1.3 SBUF1.2 SBUF1.1 SBUF1.0

C1h

— — — — —

RMS2

RMS1

RMS0 C2h

CD1 CD0 SWB — XTOFF

ALEOFF

DME1

DME0 C4h

HIP

LIP XTUP SPTA1 SPRA1 SPTA0 SPRA0

C5h

TA.7 TA.6 TA.5 TA.4 TA.3 TA.2 TA.1 TA.0 C7h

TF2 EXF2

RCLK

TCLK

EXEN2

TR2 C/

T2

CP/

RL2

C8h

— — — — — —

T2OE

DCEN

C9h

RCAP2L.7 RCAP2L.6 RCAP2L.5 RCAP2L.4 RCAP2L.3 RCAP2L.2 RCAP2L.1 RCAP2L.0

CAh

RCAP2H.7 RCAP2H.6 RCAP2H.5 RCAP2H.4 RCAP2H.3 RCAP2H.2 RCAP2H.1 RCAP2H.0

CBh

TL2.6

TL2.5 TL2.4 TL2.3 TL2.2 TL2.1 TL2.0 CCh

TH2.7 TH2.6 TH2.5 TH2.4 TH2.3 TH2.2 TH2.1 TH2.0 CDh

CY AC F0 RS1

RS0 OV F1 P D0h

SMOD_1 POR EPFI PFI WDIF WTRF EWT

RWT D8h

ACC.7 ACC.6 ACC.5 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0

E0h

— — —

EWDI

EX5

EX4 EX3 EX2 E8h

B.7 B.6 B.5 B.4 B.3 B.2 B.1 B.0 F0h

— — —

PWD1

PX5

PX4 PX3 PX2 F8h

Note: Shaded bits are timed-access protected.