3 data pointer low 0 (dpl), 4 data pointer high 0 (dph), 5 data pointer low 1 (dpl1) – Maxim Integrated High-Speed Microcontroller User Manual

Page 26: 6 data pointer high 1 (dph1), Port 0 (p0), Stack pointer (sp), Dpl1, Dph1

High-Speed Microcontroller User’s Guide

Rev: 062210

26 of 176

4.2.3 Data Pointer Low 0 (DPL)

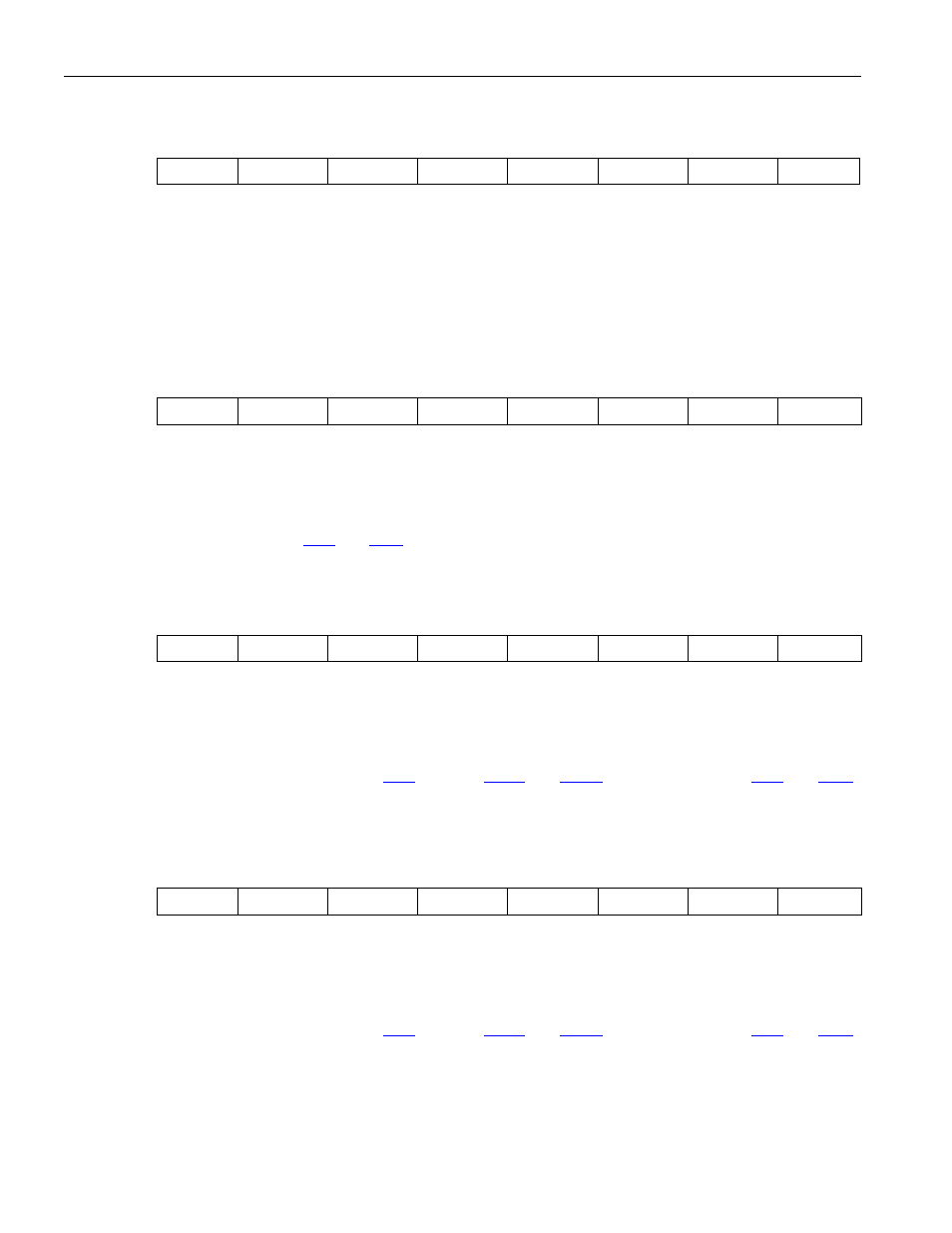

7 6 5 4 3 2 1 0

SFR 82h

DPL.7

DPL.6

DPL.5

DPL.4 DPL.3 DPL.2 DPL.1 DPL.0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

DPL.7–DPL.0

Bits 7–0

Data Pointer Low 0. This register is the low byte of the standard 80C32 16-bit data

pointer. DPL and DPH are used to point to non-scratchpad data RAM.

4.2.4 Data Pointer High 0 (DPH)

7 6 5 4 3 2 1 0

SFR 83h

DPH.7

DPH.6

DPH.5

DPH.4 DPH.3 DPH.2 DPH.1 DPH.0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

DPH.7–DPH.0

Bits 7–0

Data Pointer High 0. This register is the high byte of the standard 80C32 16-bit data

pointer.

and

are used to point to non-scratchpad data RAM.

4.2.5 Data Pointer Low 1 (DPL1)

7 6 5 4 3 2 1 0

SFR 84h

DPL1.7

DPL1.6

DPL1.5

DPL1.4 DPL1.3 DPL1.2 DPL1.1 DL1H.0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

DPL1.7—DPL1.0

Bits 7–0

Data Pointer Low 1. This register is the low byte of the auxiliary 16-bit data pointer.

When the SEL bit (

are used in place of

during DPTR operations.

4.2.6 Data Pointer High 1 (DPH1)

7 6 5 4 3 2 1 0

SFR 85h

DPH1.7

DPH1.6

DPH1.5

DPH1.4 DPH1.3 DPH1.2 DPH1.1 DPH1.0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

DPH1.7—DPH1.0

Bits 7–0

Data Pointer High 1. This register is the high byte of the auxiliary 16-bit data pointer.

When the SEL bit (

are used in place of

during DPTR operations.