Epson S1D13705 User Manual

Page 70

Page 64

Epson Research and Development

Vancouver Design Center

S1D13705

Hardware Functional Specification

X27A-A-001-10

Issue Date: 02/02/01

bits 7-0

Memory Address Offset Bits [7:0] (Landscape Modes Only)

This register is used to create a virtual image by setting a word offset between the last

address of one line and the first address of the following line. If this register is not equal to

zero, then a virtual image is formed. The displayed image is a window into the larger vir-

tual image. See Figure 8-1: “Screen-Register Relationship, Split Screen,” on page 65.

This register has no effect in SwivelView modes. See “REG[1Ch] Line Byte Count Regis-

ter for SwivelView Mode” on page 68.

.

REG[13h] bits 1-0

Screen 1 Vertical Size Bits [9:0]

REG[12h] bits 7-0

This register is used to implement the Split Screen feature of the S1D13705. These bits

determine the height (in lines) of Screen 1.

In landscape modes, if this register is programmed with a value, n, where n is less than the

Vertical Panel Size (REG[06h], REG[05h]), then lines 0 to n of the panel contain Screen 1

and lines n+1 to REG[06h], REG[05h] of the panel contain Screen 2. See Figure 8-1:

“Screen-Register Relationship, Split Screen,” on page 65. If Split Screen is not desired,

this register must be programmed greater than, or equal to the Vertical Panel Size,

REG[06h] and REG[05h].

In SwivelView modes this register must be programmed greater than, or equal to the Verti-

cal Panel Size, REG[06h] and REG[05h]. See “SwivelView™” on page 77.

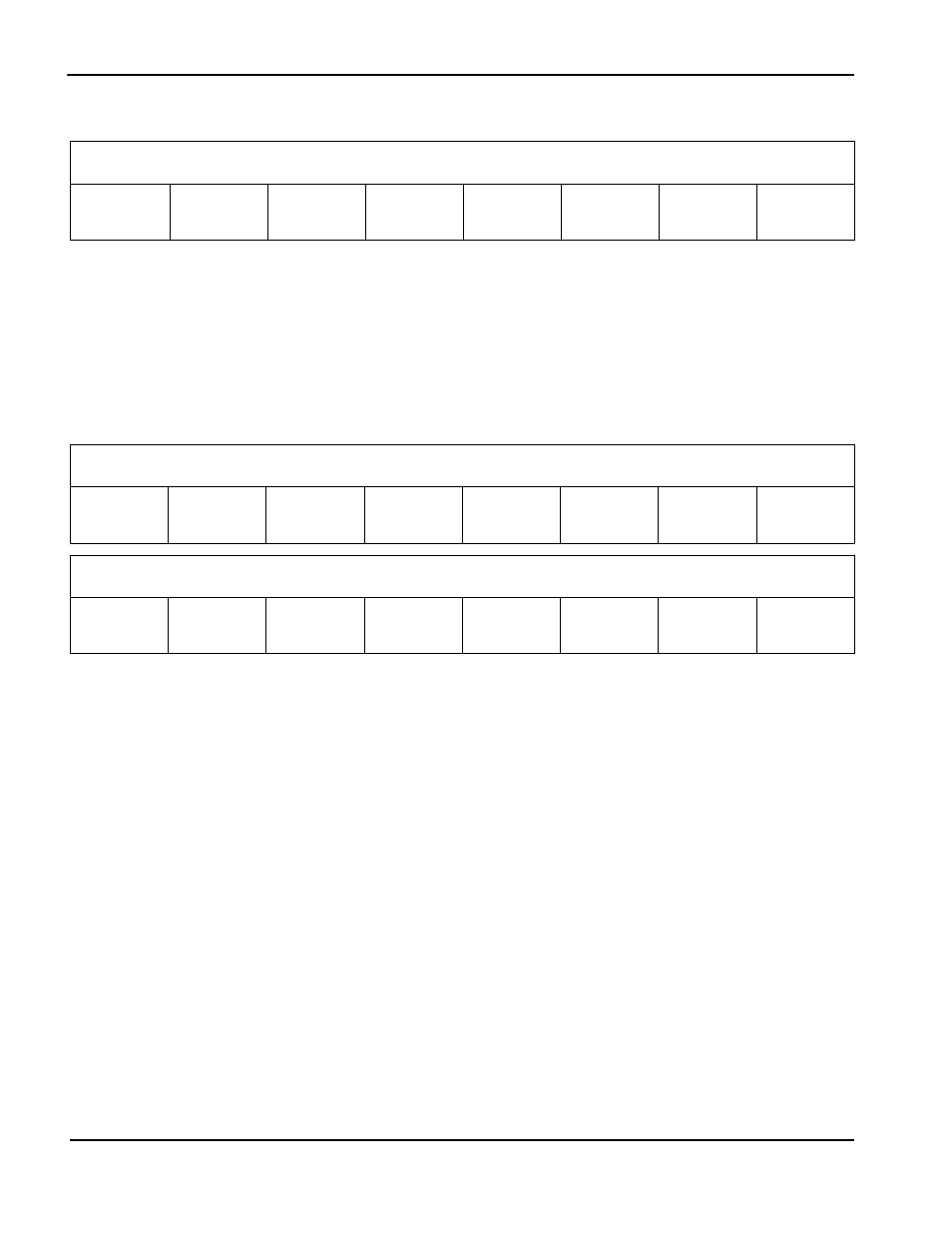

REG[11h] Memory Address Offset Register

Address = 1FFF1h

Read/Write

Memory

Address

Offset Bit 7

Memory

Address

Offset Bit 6

Memory

Address

Offset Bit 5

Memory

Address

Offset Bit 4

Memory

Address

Offset Bit 3

Memory

Address

Offset Bit 2

Memory

Address

Offset Bit 1

Memory

Address

Offset Bit 0

REG[12h] Screen 1 Vertical Size Register (LSB)

Address = 1FFF2h

Read/Write

Screen 1

Vertical Size

Bit 7

Screen 1

Vertical Size

Bit 6

Screen 1

Vertical Size

Bit 5

Screen 1

Vertical Size

Bit 4

Screen 1

Vertical Size

Bit 3

Screen 1

Vertical Size

Bit 2

Screen 1

Vertical Size

Bit 1

Screen 1

Vertical Size

Bit 0

REG[13h] Screen 1 Vertical Size Register (MSB)

Address = 1FFF3h

Read/Write

n/a

n/a

n/a

n/a

n/a

n/a

Screen 1

Vertical Size

Bit 9

Screen 1

Vertical Size

Bit 8