Figure 21: pc card read cycle, Figure 22: pc card write cycle – Epson S1D13705 User Manual

Page 445

Epson Research and Development

Page 9

Vancouver Design Center

Interfacing to the PC Card Bus

S1D13705

Issue Date: 01/02/13

X27A-G-009-02

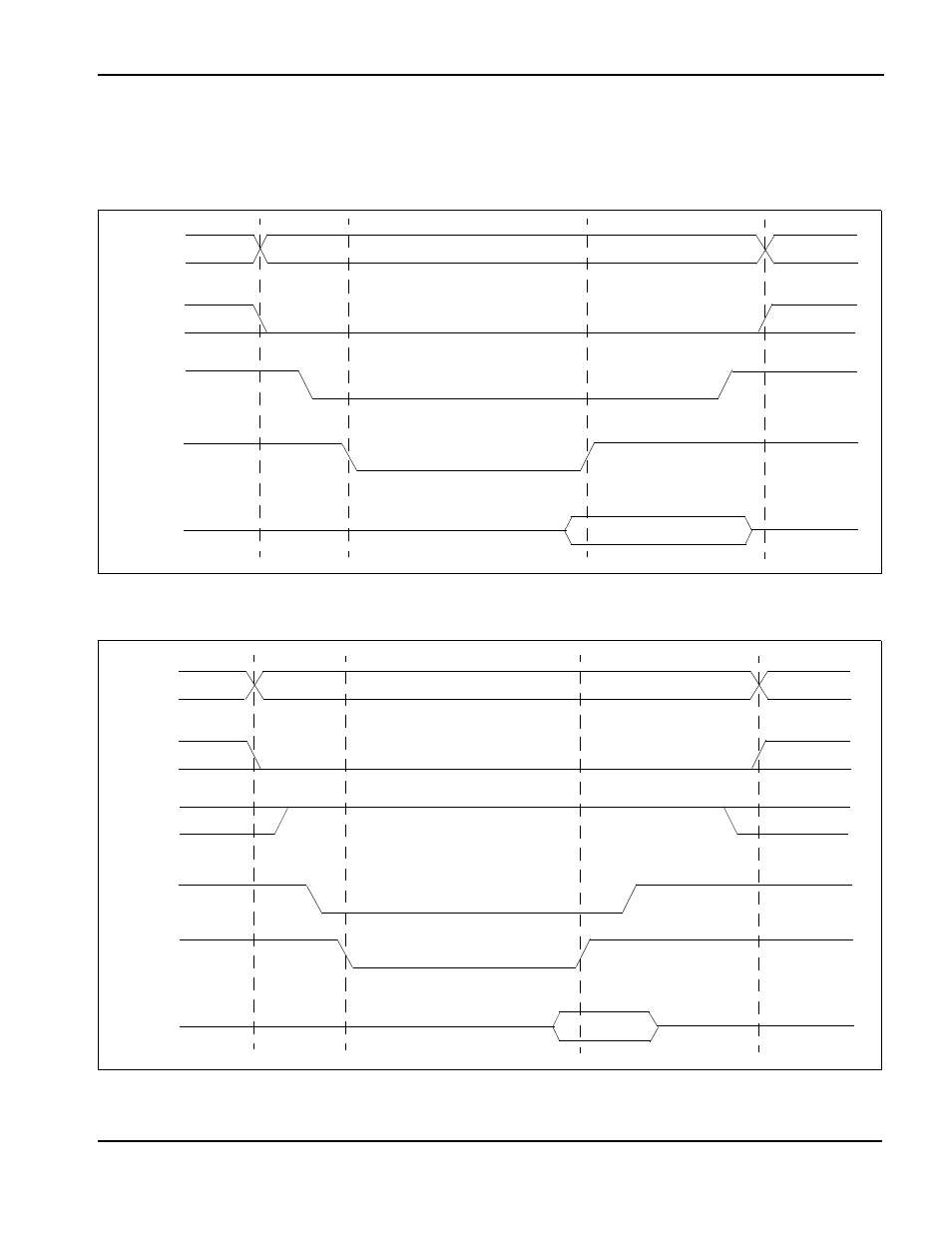

During a read cycle, OE# (output enable) is driven low. A write cycle is specified by

driving OE# high and driving the write enable signal (WE#) low. The cycle can be

lengthened by driving WAIT# low for the time needed to complete the cycle.

Figure 2-1: and Figure 2-2: illustrate typical memory access cycles on the PC Card bus.

Figure 2-1: PC Card Read Cycle

Figure 2-2: PC Card Write Cycle

A[25:0]

CE1#

OE#

WAIT#

ADDRESS VALID

DATA VALID

Hi-Z

Hi-Z

D[15:0]

REG#

CE2#

Transfer Start

Transfer Complete

A[25:0]

CE1#

OE#

WAIT#

ADDRESS VALID

DATA VALID

Hi-Z

Hi-Z

D[15:0]

REG#

CE2#

Transfer Start

Transfer Complete

WE#