9 dual color 8-bit panel timing, Figure 723: dual color 8-bit panel timing, Dual color 8-bit panel timing – Epson S1D13705 User Manual

Page 56: Figure 7-23: dual color 8-bit panel timing

Page 50

Epson Research and Development

Vancouver Design Center

S1D13705

Hardware Functional Specification

X27A-A-001-10

Issue Date: 02/02/01

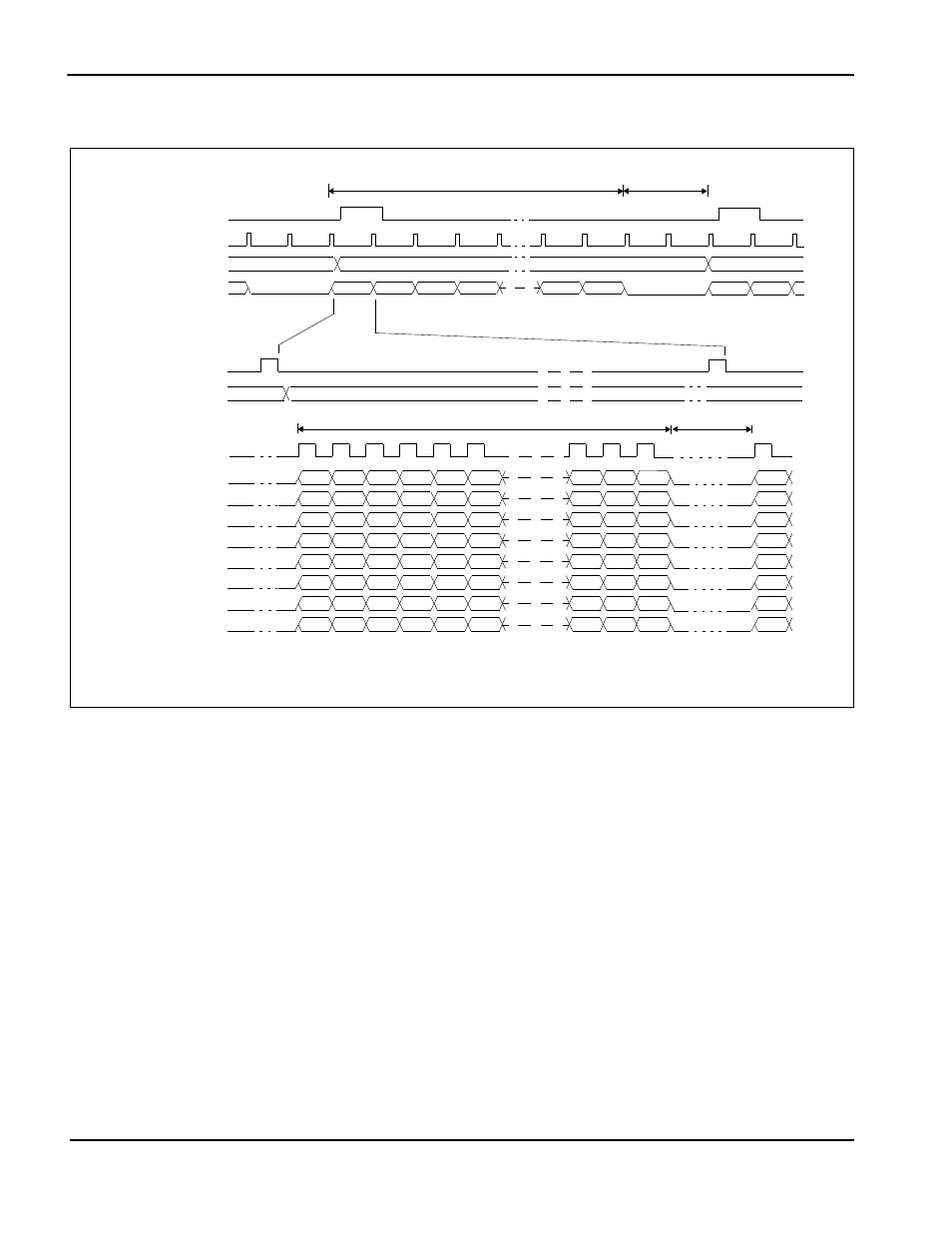

7.3.9 Dual Color 8-Bit Panel Timing

Figure 7-23: Dual Color 8-Bit Panel Timing

VDP =

Vertical Display Period

= (REG[06h] bits 1-0, REG[05h] bits 7-0) + 1 Lines

VNDP =

Vertical Non-Display Period

= REG[0Ah] bits 5-0 Lines

HDP =

Horizontal Display Period

= ((REG[04h] bits 6-0) + 1) x 8Ts

HNDP =

Horizontal Non-Display Period

= (REG[08h] + 4) x 8Ts

VDP

FPLINE

FPDAT[7:0]

FPFRAME

FPLINE

DRDY (MOD)

DRDY (MOD)

VNDP

1-R1

1-G1

1-B1

1-R2

1-G 2

1-B2

1-R 3

1-G3

1-B3

1-R4

1-G4

1-B4

1-R 5

1-G5

1-B 5

1-R6

1-G6

1-B6

1-R7

1-G7

1-R8

1-G8

1-B8

1-B639

1-R640

1-G640

1-B640

2 41-

B639

241-

R640

241-

G640

2 41-

B640

241-R 1

241-G1

241-B1

241-R 2

241-G2

24 1-B2

241-R3

241-G3

241-B 3

241-R 4

241-G4

241-B4

241-R5

241-G 5

241-B5

241-R 6

241-G6

241-B6

241-R7

241-G7

241-B7

241-R8

241-G8

241-B8

1-B7

FPSHIFT

HDP

HNDP

* Diagram drawn with 2 FPLINE vertical blank period

Example timing for a 640x480 panel

LINE 1/241

LINE 2/242

LINE 239/479 LINE 240/480

LINE 1/241

FPDAT6

FPDAT5

FPDAT4

FPDAT3

FPDAT2

FPDAT1

FPDAT0

FPDAT7