Echelon Series 6000 Chip databook User Manual

Page 93

B. The European comité européen de normalisation electrotechnique

(CENELEC) EN

55022 standard and the international comité international spécial des perturbations

radioélectriques

(CISPR) 22 standard both require similar compliance, and most countries

throughout the world require compliance with similar regulations.

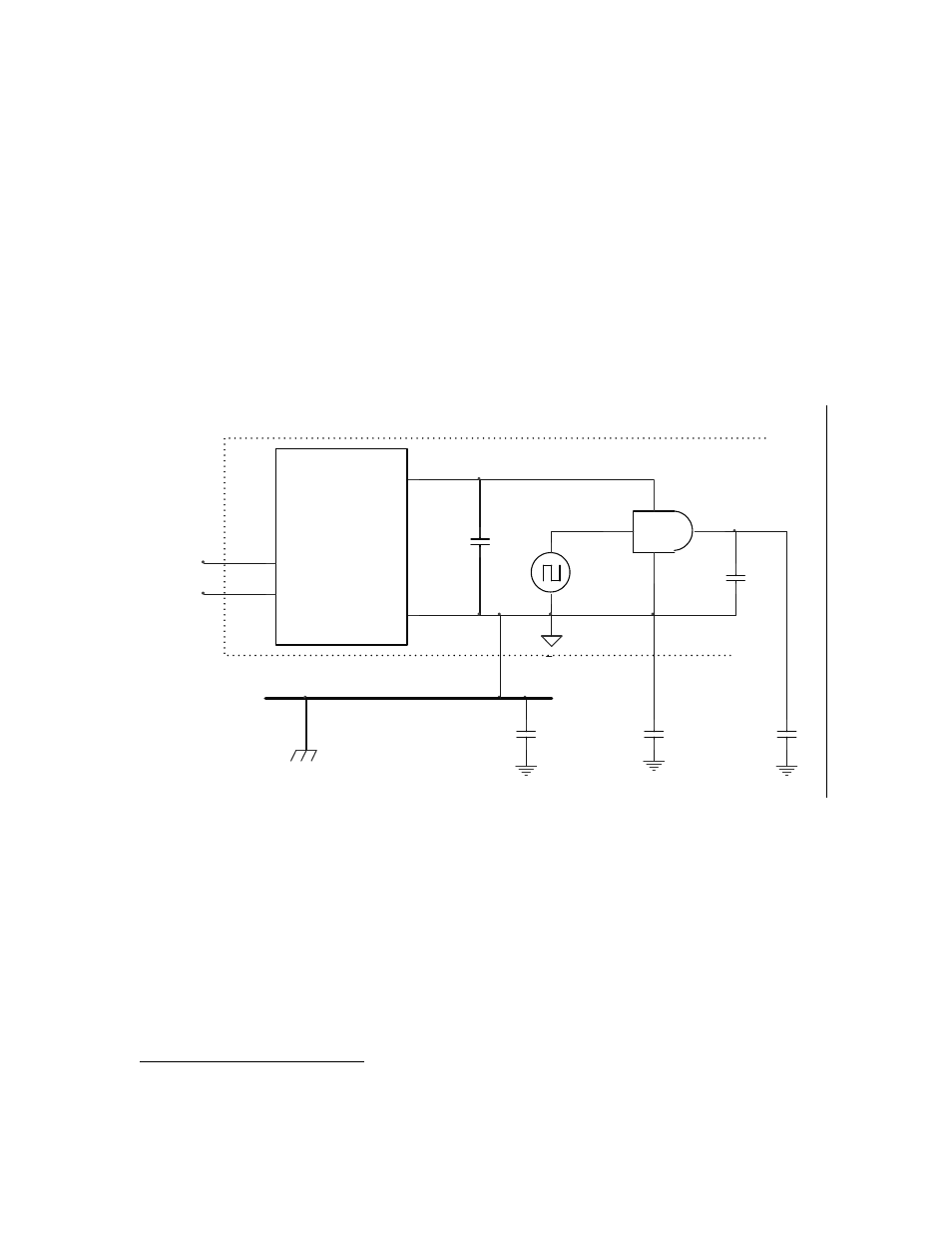

A typical Series 6000 device has several digital I/O signals that switch in the kHz to MHz

range. These signals generate voltage noise near the signal traces, and also generate current

noise in the signal traces and power supply traces. The goal of good device design is to keep

this voltage and current noise from coupling out of the product’s package. Thus, careful PCB

layout can ensure that a Series 6000 device achieves the desired low level of EMI emissions.

It is important to minimize the leakage capacitance from circuit traces in the device to any

external pieces of metal near the device, because this capacitance provides a path for the

digital noise to couple out of the product's package. Figure 31 shows the leakage

capacitances to Earth ground from a device's logic ground (C

leak,GND

) and from a digital signal

line in the device (C

leak,SIGNAL

).

C decouple

+

-

C load

C leak, CHASSIS

C leak, GND

C leak, SIGNAL

CHASSIS

GND

Node

Logic

Ground

FT 6000

Smart

Transceiver

U1

FT 6000

VDD3V3

NETP

NETN

GND

Floating Devices on L

ON

W

ORKS

Networks

Leak Capacitances

to Earth Ground

LonWorks

Network

V gate

Figure 31. Parasitic Leakage Capacitances to Earth Ground

If the Series 6000 device is housed inside a metal chassis, that chassis likely has the largest

leakage capacitance to other nearby pieces of metal. If the device is housed inside a plastic

package, use PCB ground guarding to minimize C

leak,SIGNAL

. Effective guarding of digital

traces with logic ground reduces C

leak,SIGNAL

significantly, which reduces the level of common-

mode RF currents driven onto the network cable.

For a device mounted near a piece of metal, especially metal that is Earth grounded, any

leakage capacitance from fast signal lines to that external metal provides a path for RF

currents to flow. When V

gate

is pulled down to logic ground, the voltage of logic ground with

respect to Earth ground increases slightly. When V

gate

is pulled up to V

DD33

, logic ground is

pushed down slightly with respect to Earth ground.

6

European Committee for Electrotechnical Standardization

7

International Special Committee on Radio Interference

Series 6000 Chip Data Book

81