Echelon Series 6000 Chip databook User Manual

Page 61

•

Beta 1 Time after Transmission = 583 cycles + Transmit Interpacket Padding + Beta

2 Slot Width

•

Beta 1 Time after Reception = 565 cycles + Receive Interpacket Padding + Beta 2 Slot

Width

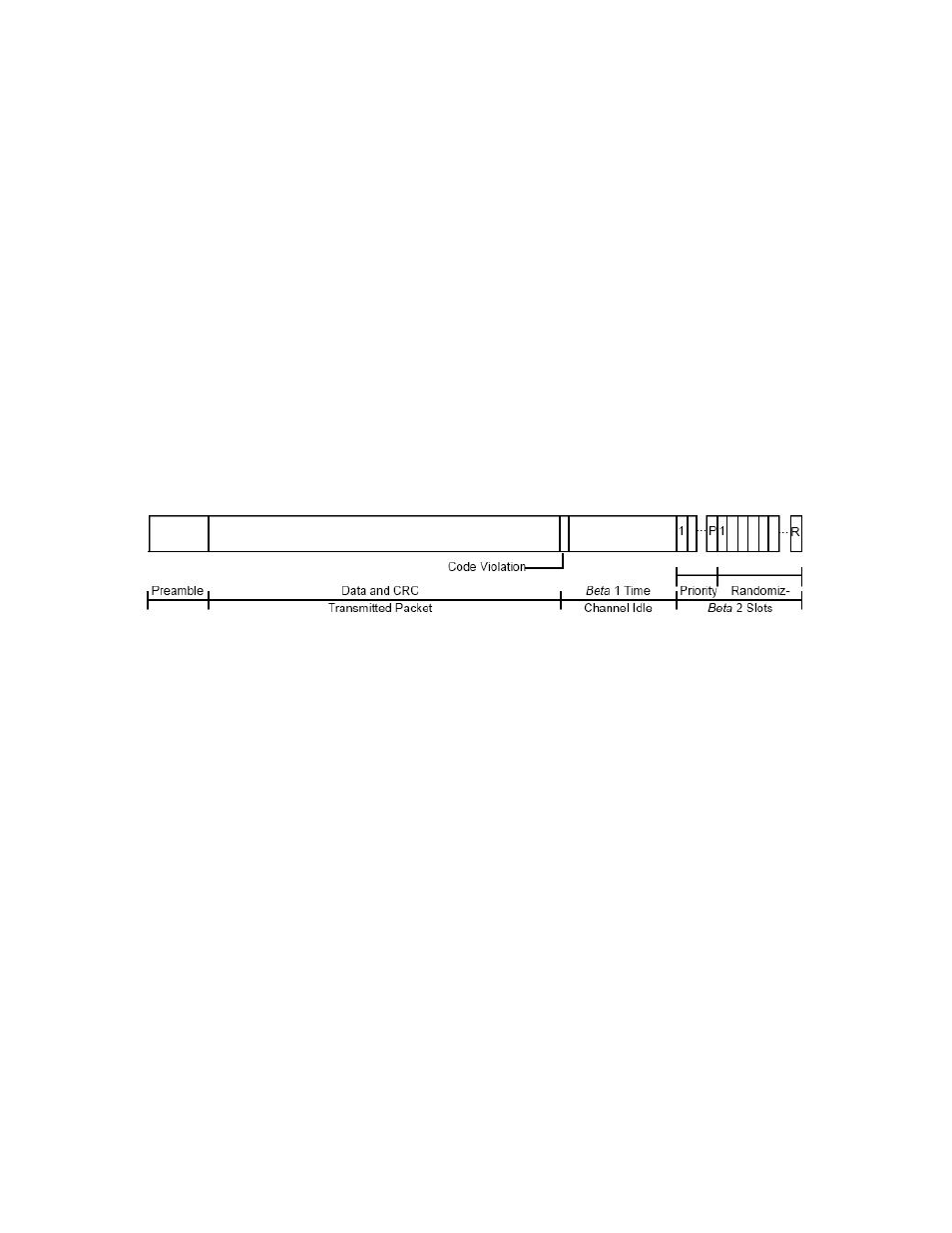

An indeterminate time is defined during the Beta 1 period in which all transitions on the

channel are ignored. This period starts following the end of any packet (transmitted or

received). Its duration is defined as follows:

•

Indeterminate Time after transmission = 313 cycles + Transmit Interpacket Padding

•

Indeterminate Time after reception = 295 cycles + Receive Interpacket Padding

Both priority (P) and non-priority slots are defined by the Beta 2 time. Devices listen to the

network prior to transmitting a packet. This prevents devices from transmitting packets on

top of each other except when the packets are initiated at nearly the same time. In addition,

devices randomize the time before they start transmitting on the network. When the

network is idle, all nodes randomize over 16 slots. As the estimated network load increases,

devices start randomizing over more slots to lower the probability of a collision. The number

of randomizing slots (R) varies from 16 up to 1008, based on “n,” the estimated channel

backlog (the number of slots is n•16 where “n” has a range of 1 to 63), as shown in Figure

Figure 18. Packet Timing

Following a packet, and prior to randomizing, devices wait for a configurable number of

priority slots to pass. Devices with priority packets and a configured priority slot transmit in

a priority slot. Use of priority substantially reduces the probability of collision. The number

of priority slots (P) is fixed for a given channel and can range from 0 to 127.

The Beta 2 time is defined by the following:

•

Oscillator frequencies and accuracies on the various network devices.

•

Number of priority slots on the channel.

•

Receive start delay — the time from when a device starts transmitting to when the

receiving device detect the start of transmission. This delay is a function of the

receive-to-transmit turnaround time of the transceiver, the bit rate and length of the

media, delay through the receiver, and initial preamble bits lost.

•

For special-purpose mode transceivers, framing delays between the Neuron Chip and

the transceiver.

For the receiver to detect the edge transitions, two windows are set up for each bit period, T.

The first window is set at T/2 and determines if a zero is being received. The second window

is at T and defines a one. This transition then sets up the next two windows (T/2 and T). If

no transition occurs, a Differential Manchester code violation is detected and the packet is

assumed to have ended.

Table 18 shows the width of this window. If a transition falls outside of either window, it is

not detected. Timing instability of the transitions, known as jitter, can be caused by changes

Series 6000 Chip Data Book

49