Comparison with series 3100 clocks – Echelon Series 6000 Chip databook User Manual

Page 74

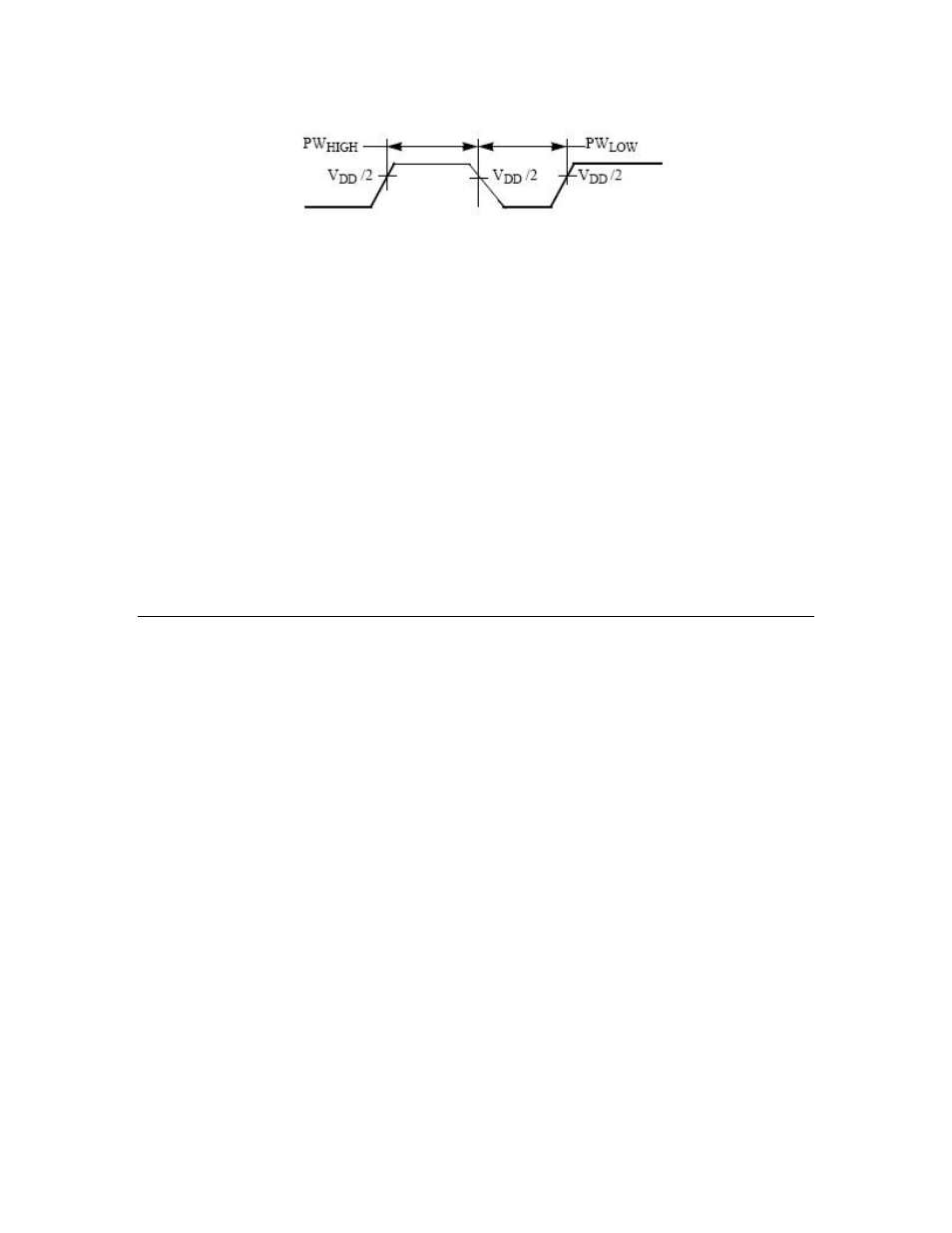

Figure 25. Test Point Levels for XIN Duty-Cycle Measurements

To ensure proper oscillator startup, the equivalent series resistance specification for the

crystal should be ≤50 Ω, and the crystal shunt capacitance should be no greater than 7 pF.

A Series 6000 chip requires a clock frequency with a total accuracy of ±200 ppm over the full

range of component tolerances and operating conditions, including oscillator tolerance,

crystal tolerance, PCB and capacitor variation, and aging. Variation within the Series 6000

chip uses a portion of the overall ±200 ppm budget. Its duty cycle symmetry must be no

worse than 60/40%. In addition, the voltage swing of the clock signal must be within the

GND and V

DD33

supply rails of the Series 6000 chip. This clock can be provided by connecting

an appropriate parallel resonant crystal to the XIN and XOUT pins of the Series 6000 chip,

as shown in Figure 24.

The remaining portion of the error budget allocated for total crystal uncertainty is ±85 ppm

(assuming that the selected crystal has a load capacitance specification that matches the

circuit loading). Total crystal uncertainty is the combination of the crystal’s initial frequency

tolerance plus its temperature and aging tolerances. Note that a typical crystal aging

specification is 5 ppm/yr but, because the aging effect tends to follow a logarithmic curve,

aging over a 10 year span is commonly in the range of 10 to 15 ppm (contact individual

crystal vendors for detailed specifications).

Comparison with Series 3100 Clocks

For Series 3100 chips, you specified the value of the system clock through the use of a

specific external crystal or oscillator (for example, a 10 MHz crystal). For Series 6000

devices, you specify the system clock rate through software tools (the IzoT NodeBuilder

Development Tool). For a Series 6000 device, the external clock is always a 10 MHz crystal,

but the internal system clock rate can vary from 5 MHz to 80 MHz.

Internally, a Series 3100 chip divided the external crystal’s frequency by 2 to obtain an

internal system clock rate; thus, a 10 MHz external crystal provided a 5 MHz internal

system clock rate. However, a Series 6000 chip multiplies the external crystal’s 10 MHz

frequency by a value specified in the device’s hardware template to specify the internal

system clock rate; thus, a multiplier value of 1 yields a 10 MHz internal system clock rate,

and a multiplier value of 8 yields an 80 MHz internal system clock rate. Valid multiplier

values are ½, 1, 2, 4, and 8. Note that a for a multiplier value of ½, the Series 6000 chip

actually runs at 10 MHz (as if a multiplier of 1 were specified), but the Neuron system

firmware schedules the application such that the application runs at 5 MHz.

Because the internal system clock rate is multiplied, rather than divided, a Series 6000 chip

of a specific system clock rate can be considered to be approximately twice as fast as an

equivalent Series 3100 chip (for example, an FT 6000 Smart Transceiver with a system clock

of 20 MHz is approximately twice as fast as FT 3150 Smart Transceiver with an input clock

of 20 MHz). The difference is approximate because a specific application on a Series 6000

device might run more than twice (or less than twice) as fast it would on a Series 3100 device

due to variations in the hardware and software that are required by the Neuron architecture

for Series 6000 devices.

62

Hardware Resources