Pin connections – Echelon Series 6000 Chip databook User Manual

Page 51

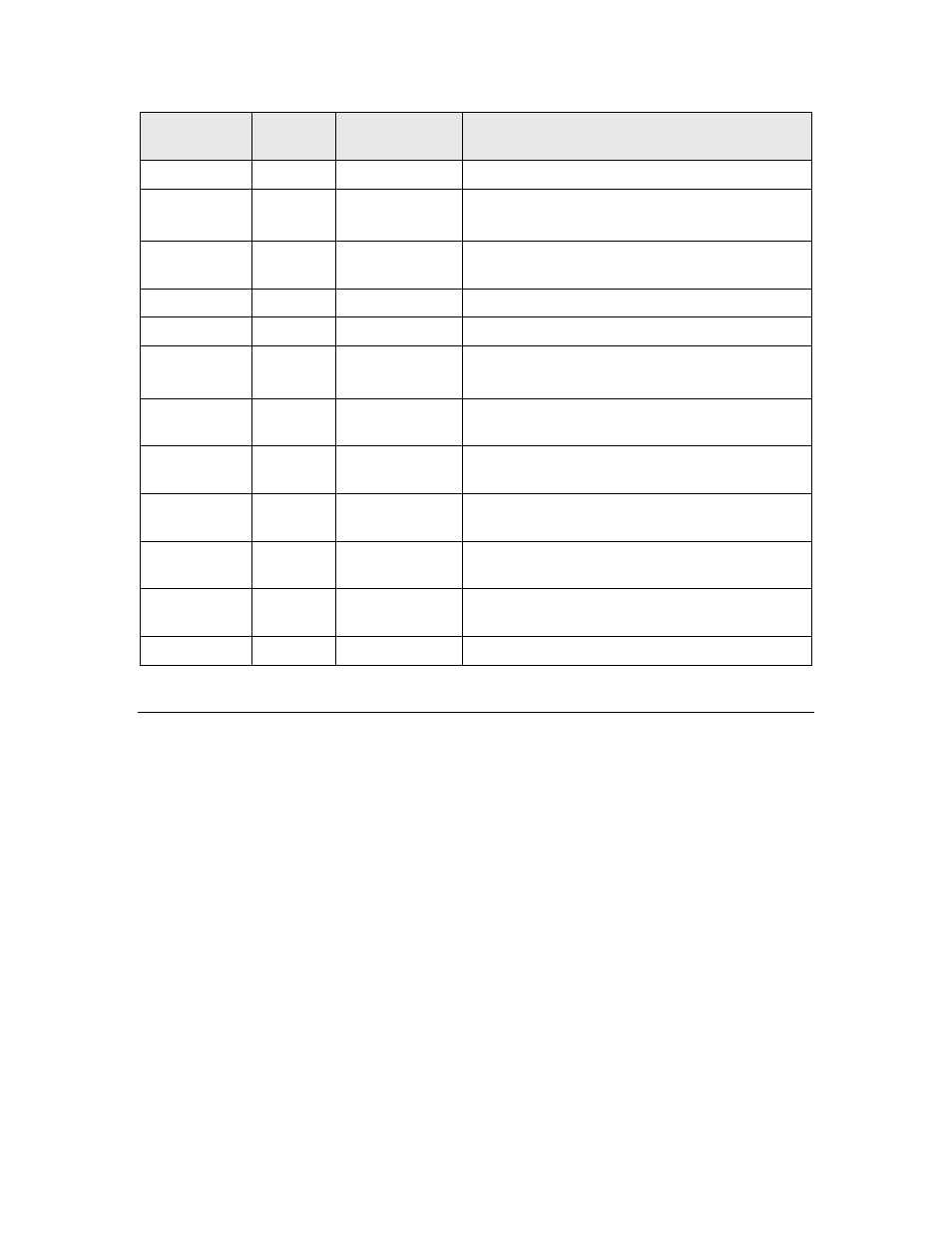

Name

Pin

Number Type

Description

CP3

38

Comm

Do Not Connect

CP4

39

Comm

Single-Ended Mode: Collision detect

Special-Purpose Mode: Frame clock

CS0~

40

Digital I/O for

Memory

SPI slave select 0 (active low)

VDD3V3

41

Power

3.3 V Power

VDD3V3

42

Power

3.3 V Power

SDA_CS1~

43

Digital I/O for

Memory

I

2

C: serial data

SPI: slave select 1 (active low)

VDD1V8

44

Power

1.8 V Power Input

(from internal voltage regulator)

SCL

45

Digital I/O for

Memory

I

2

C serial clock

MISO

46

Digital I/O for

Memory

SPI master input, slave output (MISO)

SCK

47

Digital I/O for

Memory

SPI serial clock

MOSI

48

Digital I/O for

Memory

SPI master output, slave input (MOSI)

PAD

49

Ground Pad

Ground

Pin Connections

This section describes the electrical connections for the various pins on a Series 6000 chip.

Unless specified otherwise, the connections apply to both the FT 6000 Smart Transceiver and

the Neuron 6000 Processor.

See Appendix E, Example Schematic, for a more complete example schematic for an FT 6000

Smart Transceiver.

Connect the VDD3V3 pins (8, 18, 29, 30, 41, and 42) to V

DD33

. Also connect the AVDD3V3

pin (31) to an analog V

DD33

source, if different from the digital V

DD33

source. In general, the

VDD3V3 pins and the AVDD3V3 pin connect to the same V

DD33

source. In addition, connect

decoupling capacitors to the VDD3V3 pins, as shown in Figure 10.

Series 6000 Chip Data Book

39