Device support – Echelon Series 6000 Chip databook User Manual

Page 40

of this area (e.g., network configuration tables). This area comprises either 2 or 4 flash

sectors of 4KB each depending on the demands of the application. For the 2 sector case, this

area can be modified at most 200,000 times over the device’s lifetime. This works out to

about one update per hour over a 20-year lifetime.

Note that the data is committed to flash using a 500 millisecond hold down timer. So, if you

make multiple modifications to NVM in quick succession, it will typically only result in one

erase/write cycle. Note that if you make modifications to NVM and then do a controlled reset

before the timer expires, the data is written immediately prior to the reset.

Device Support

A Series 6000 device requires 512KB or greater flash devices that meet the requirements as

described below Furthermore, the flash device must use 4KB sectors and be capable of write-

protecting the lower half of the address space.

Larger flash sizes are supported and allow for larger system images and larger application

code, data and logs. Series 6000 chips have no user-accessible on-chip ROM or non-volatile

writable memory. A default system image is contained in on-chip ROM, but its sole purpose

is to support the downloading of the system image over the network in a factory or lab

setting. Flash memory for use with Series 6000 chips must support the following features:

•

SPI serial interface, minimum clock rate of 20 MHz

•

24-bit addressing

•

At least 4 Mb capacity

•

3.3VCC operation with a minimum 2.7 VCC

•

Operating temperature range of -40 °C to +85 °C

•

>100,000 erase cycles, 20 year retention data

•

Status register with BUSY flag at D0

•

4 KB erasable sector size

•

256-byte page write architecture (up to 256 bytes written inside a single ~CS

assertion

•

Block write-protection capability via Status Register write, at least 4 block protect

bits, with capability of protecting first half of the device

•

Block write protect setting using these bits:

0bxx1011xx (4 Mb), 0bxx1100xx (8

Mb), 0bxx1101xx (16 Mb), 0bxx1110xx (32 Mb)

•

JEDEC ID reporting, including device capacity in the 3

rd

byte

•

Identical command set for all implemented commands listed below:

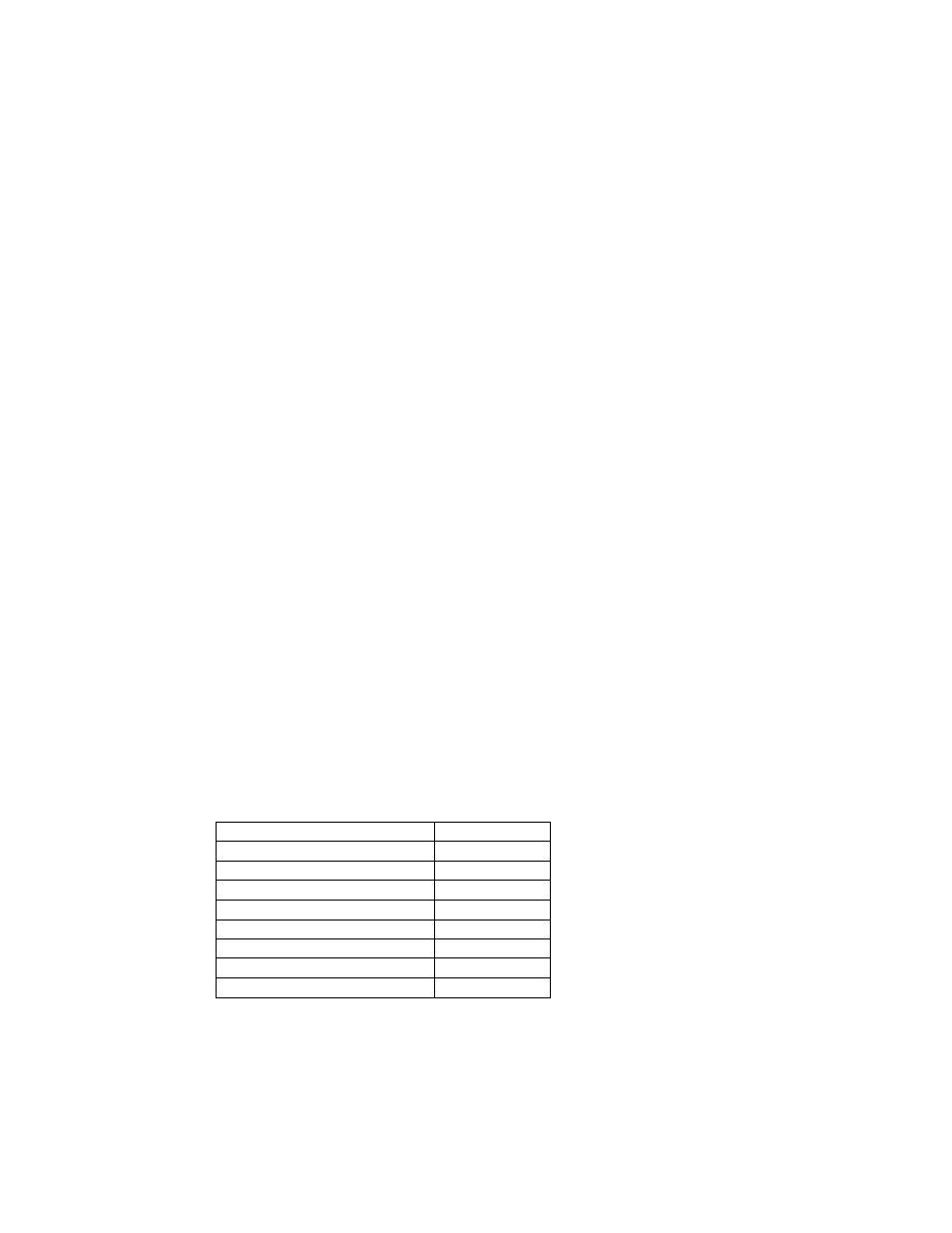

Command

Value

Write Enable

06h

Read Status Reg

05h

Write Status Reg

01h

Read Data

03h

Page Program (write)

02h

4KB Sector Erase

20h

Chip Erase

C7h

JEDEC ID

9Fh

Echelon has qualified the following SPI flash memory devices for use with a Series 6000

device:

•

Winbond W25X40CL 4 M-bit 2.3 V minimum SPI serial flash memory

•

Winbond W25Q80BV 8 M-bit 2.7 V minimum SPI serial flash memory

28

Hardware Resources