Non-volatile memory integrity – Echelon Series 6000 Chip databook User Manual

Page 39

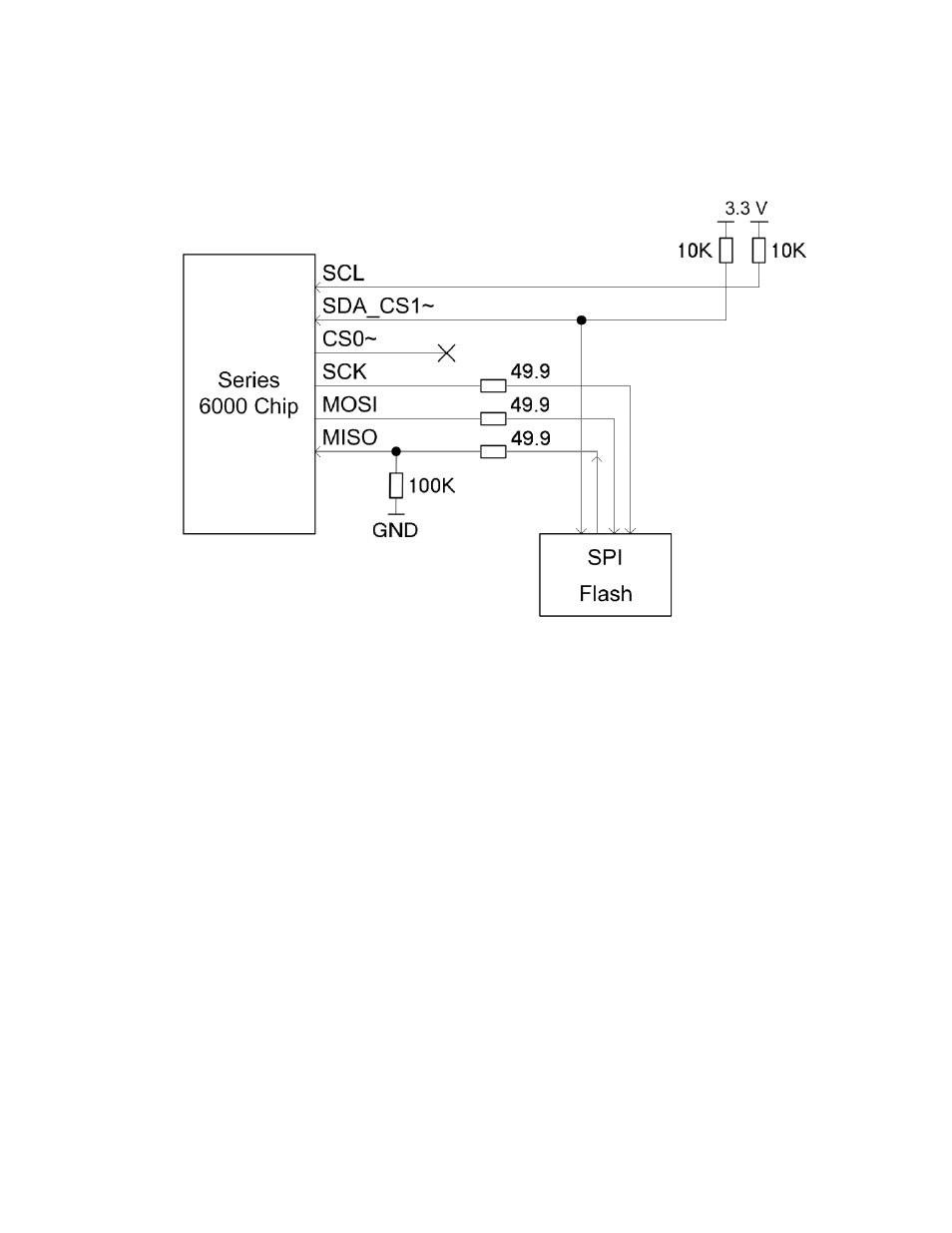

A Series 6000 chip is always the master SPI device; any external NVM devices are always

slave devices. Multimaster configurations are not supported.

Figure 7. SPI Memory Interface

Series 6000 devices support the 3-byte addressing mode for SPI flash devices.

The SPI protocol defines four modes of operation; each mode specifies different behavior for

flow control on the data bus with respect to the clock signal polarity (CPOL) and phase

(CPHA). A Series 6000 device uses SPI Mode 0: CPOL is 0, CPHA is 0, and the SCK line is

idle low. For this mode, the Series 6000 chip latches in data on the rising edge of the SCK

line, and is output on the falling edge of the SCK line. Note that the 49.9 Ohm and 100k

Ohm resistors shown in the figure are generally not needed, and can be omitted.

A Series 6000 chip runs the SPI protocol from the serial memory interface at 20 MHz for

reads and 2.5 MHz for writes.

Non-Volatile Memory Integrity

The areas labeled Network Image and Application NVM (see Figure 6. Series 6000 Chip

Memory Map) are written out to flash in an all or nothing fashion. This is accomplished by

having multiple copies of the data, an active and a standby. When updating, the standby is

updated and only once that is completed does it become active. Therefore, when changing

NVM from state X to state Y, were a power cycle to occur during the process, you will either

end up in state X or state Y, but not some intermediate (corrupted) version.

The maximum allowed size of this area is 8KB. This means that the typical application non-

volatile data will be limited to somewhere in the range of 6 to 7KB depending on other uses

Series 6000 Chip Data Book

27