External serial memory interface, Serial peripheral interface (spi) – Echelon Series 6000 Chip databook User Manual

Page 38

The memory map divides the Series 6000 chip’s physical RAM into the following types of

logical memory:

•

System Image (0x0000 to __image_end (system image dependent)) — This area is

initially a copy of the system firmware image from the physical ROM but this is

overwritten with a system image from flash later in the boot process. This area is

write-protected so that an application cannot alter the system firmware.

•

Application Resident Code/Data (from __image_end+1 up to a variable address) —

The size of this area is determined at application link time.

•

Transient Code – The size of this area is determined at application link time. By

default, most code in an application is “transient” which means it is brought into this

area from flash on demand. There is some system image transient code as well that

shares this area.

•

Application NVM – The size of this area is determined at application link time. The

maximum size of this area is 6KB. This area is brought in from flash at boot time

and written back to flash as it is modified.

•

System RAM (2 KB at addresses 0xE800 to 0xEFFF) — This area holds system data,

stack segments, buffers and select application data.

•

Mandatory NVM (2 KB at addresses 0xF000 to 0xF7FF) — This area is shadowed

from the mandatory 2 KB of NVM, and holds device configuration data.

•

Reserved memory (2 KB at addresses 0xF800 to 0xFFFF) — This area is reserved for

system use.

External Serial Memory Interface

The interface for accessing off-chip non-volatile memory (NVM) is a serial interface that uses

the serial peripheral interface (SPI).

Serial Peripheral Interface (SPI)

The serial peripheral interface (SPI) protocol for the Series 6000 chip uses the pins listed in

table 11 and shown in Figure 7.

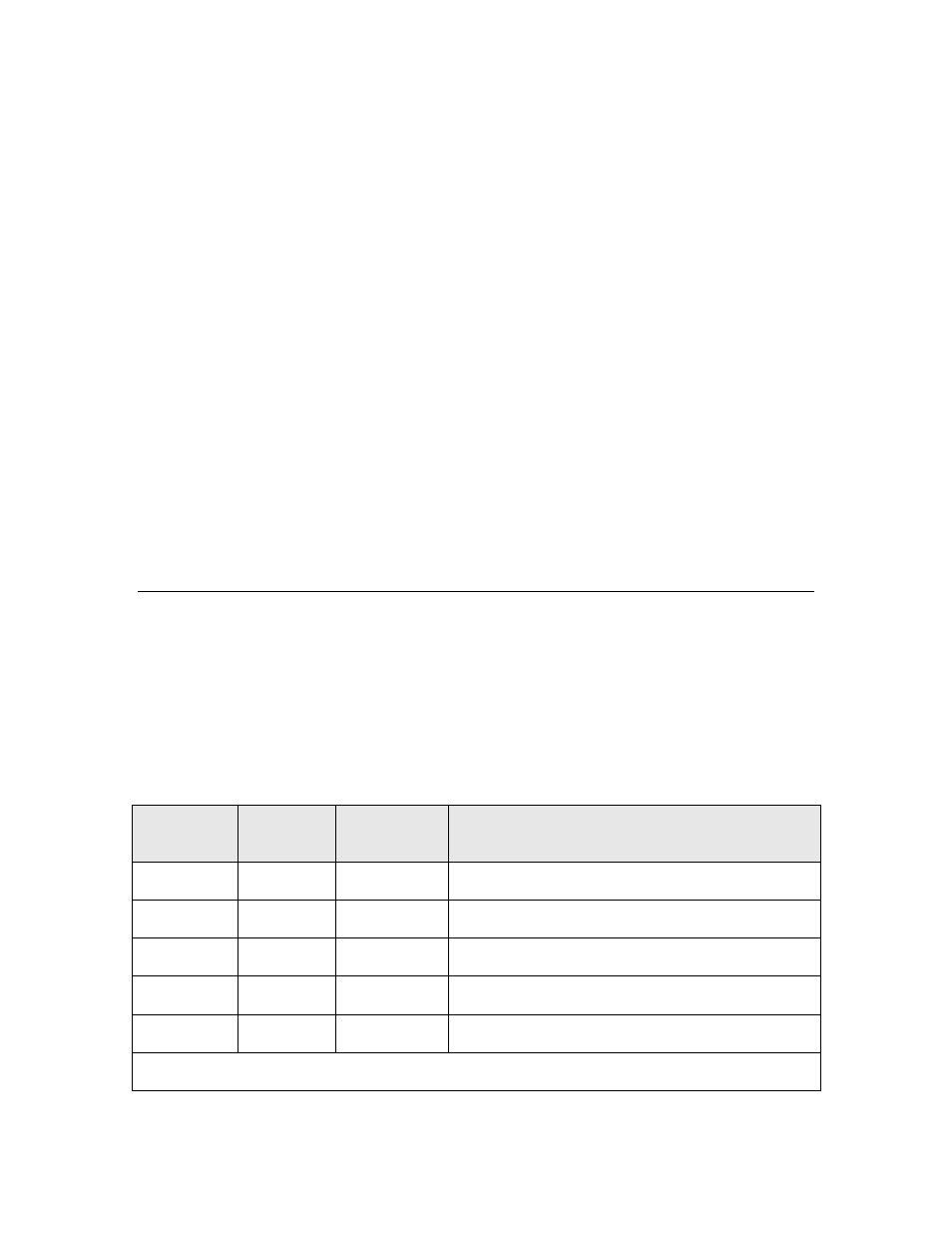

Table 11. Memory Interface Pins for the SPI Protocol

Pin

Number

Pin Name Direction

Description

Pin 40

CS0~

Output

First slave-select (SS) signal

Pin 43

SDA_CS1~ Bidirectional Second slave-select (SS) signal

Pin 46

MISO

Input

Master Input, Slave Output (MISO) signal

Pin 47

SCK

Output

Serial clock (SCK) signal

Pin 48

MOSI

Output

Master Output, Slave Input (MOSI) signal

Note: Signal direction is from the point of view of the Series 6000 chip.

These pins are 3.3 V pins, and are 5 V tolerant.

26

Hardware Resources