Echelon Series 6000 Chip databook User Manual

Page 133

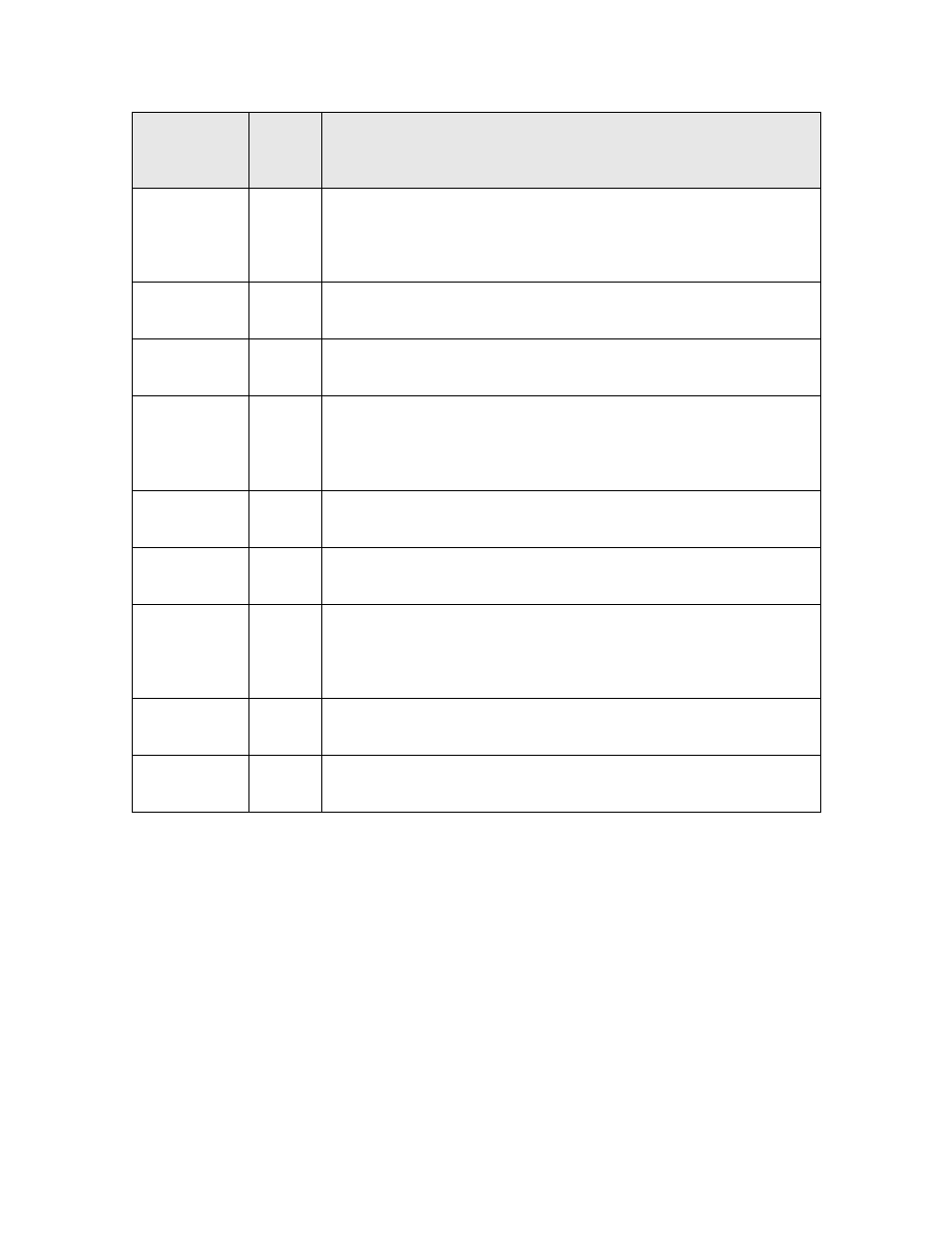

Check

When

Complete

Item

Description

CC10

Capacitors (30 pF 5% 50V NPO) are placed at the XIN and XOUT

pins (23 and 24), as described in Clock Requirements. Each

capacitor is placed directly adjacent to the XIN and XOUT pins,

on the top layer of the PCB, with a short connection to ground.

CC11

A feedback resistor (1 MΩ) is added across the XIN and XOUT

pins (23 and 24), as described in Clock Requirements.

CC12

A series resistor (200 Ω) is added at the XOUT pin (24), as

described in Clock Requirements.

CC13

Other than the crystal, the capacitors, series resistor, and the

feedback resistor, there are no other connections to the XIN pin.

The XOUT pin can optionally drive a CMOS buffer, as described

CC14

The VDDPLL pin (25) is connected to the VOUT1V8 pin (27) with

an associated chip ferrite bead, as described in Pin Connections.

CC15

The GNDPLL pin (26) is connected to GND with an associated

chip ferrite bead, as described in Pin Connections.

CC16

Stabilizing capacitors (0.01 µF 10% 50V X7R and 0.1 µF 10% 16V

X7R) are added across the PLL pins (pins 25 and 26), as described

in Pin Connections. Each capacitor is placed directly adjacent to

the PLL pins, on the top layer of the PCB.

CC17

The connections for the external memory parts meet the

requirements specified in Device Support

CC18

The JTAG TCK pin (19) includes a pullup resistor (4.99 kΩ) to

V

DD3

, as described in Pin Connections.

Series 6000 Chip Data Book

121