Table 8 – Echelon Series 6000 Chip databook User Manual

Page 32

in the Neuron Assembly language. The Neuron C compiler can optionally produce an

assembly listing, and examining this listing can help the programmer to optimize the Neuron

C source code. See the Neuron Assembly Language Reference for more information about the

processor instructions.

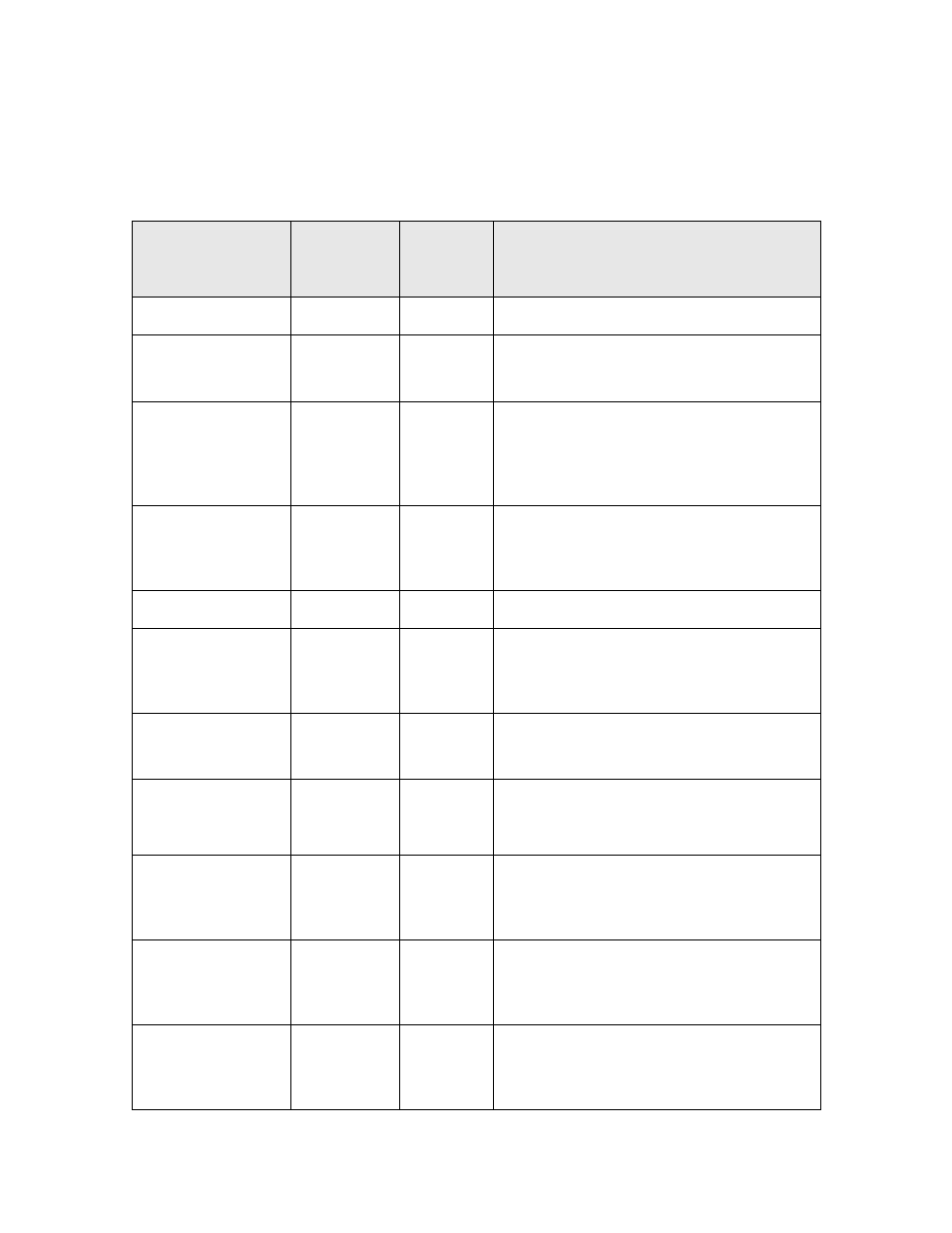

Table 8. Program Control Instructions

Instruction

Instruction

Size

(Bytes)

CPU

Cycles

Required Description

NOP

1

1

No operation

SBR

1

1

Short unconditional branch

Offset: 0 to 15.

BR

BRC

BRNC

2

2

Branch

Branch on carry

Branch on not carry

Offset: –128 to +127.

SBRZ

SBRNZ

1

3

Short branch on TOS zero

Short branch on TOS not zero

Offset: 0 to 15. Drops TOS.

BRF

3

4

Unconditional branch far

BRZ

BRNZ

2

4

Branch on TOS zero

Branch on TOS not zero

Offset: –128 to +127. Drops TOS.

RET

1

5

Return from subroutine.

Drops two bytes from return stack.

BRNEQ

3

4 / 6

(taken /

not taken)

Branch if TOS not equal

Offset: –128 to +127. Drops TOS if equal.

DBRNZ

2

5

Decrement [RSP] and branch if not zero

Offset: –128 to +127. If not taken, drops

one byte from return stack.

CALLR

2

5

Call subroutine relative

Offset: –128 to +127. Pushes two bytes to

return stack.

CALL

2

6

Call subroutine

Address in low 8 KB. Pushes two bytes to

return stack.

20

Hardware Resources