Echelon Series 6000 Chip databook User Manual

Page 63

restricted protocol that Echelon licenses for use only when the Neuron Chip and transceiver

are sold as one unit. For more details, contact Echelon Support.

When the special-purpose mode (3.3 V) is used, the Neuron 6000 Processor and the

transceiver use a protocol that consists of the Neuron 6000 Processor and the transceiver

each exchanging 16 bits (8 bits of status and 8 bits of data; see Figure 19) simultaneously

and continuously at rates up to 20.0 Mbps (when the Neuron Chip’s system clock is 80 MHz).

The 20.0-Mbps bit rate allows time-critical flags, such as a Carrier Detect, to be exchanged

across the interface with network bit rates up to 625 kbps. The maximum bit rate is 625

kbps because of the overhead associated with the handshaking.

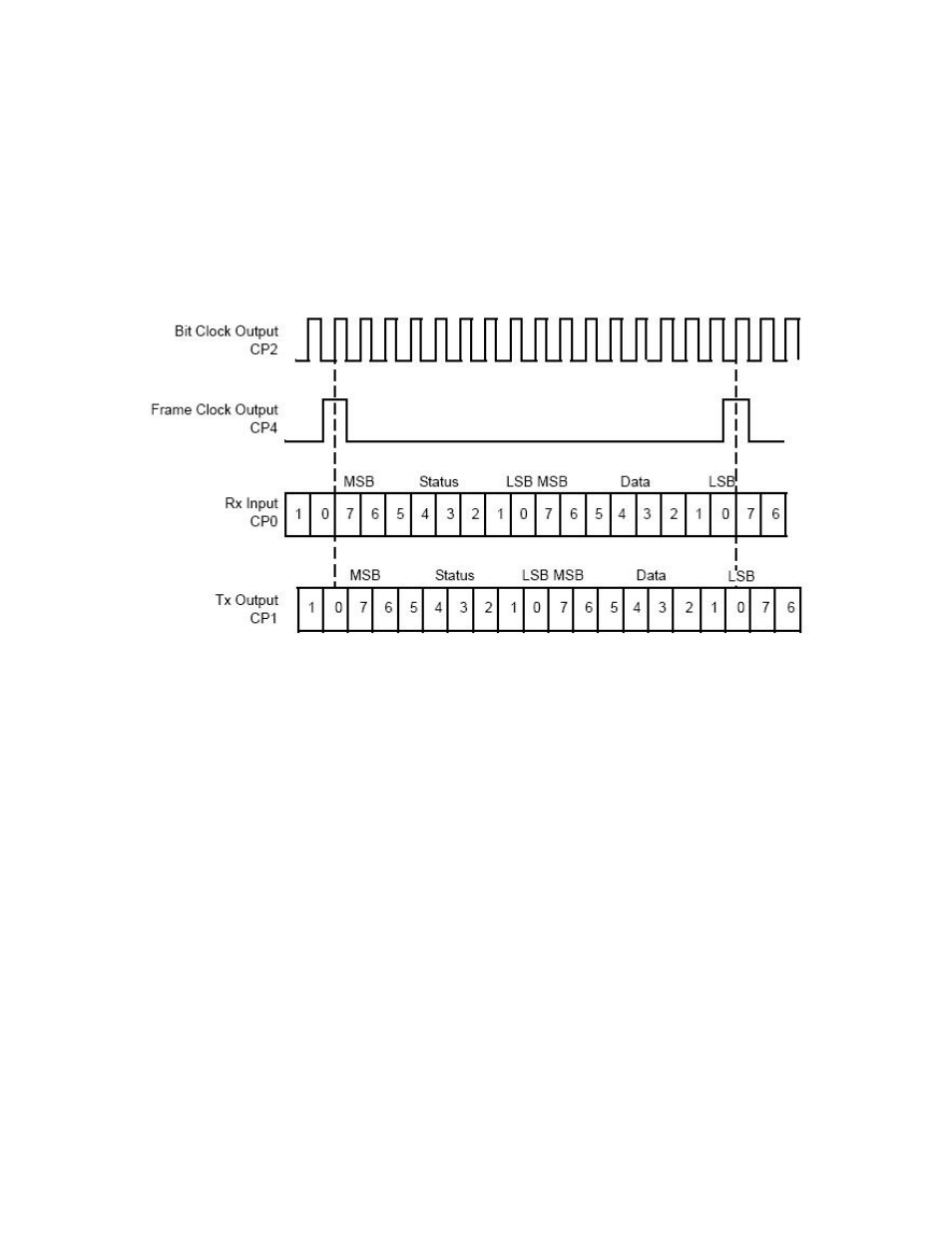

Figure 19. Special-Purpose Mode Data Format

The Neuron Chip communicates with the transceiver through its CP[4:0] pins. CP4 and CP2

are synchronizing clocks generated by the Neuron Chip: CP4 is a frame clock, and CP2 is a

bit clock. CP0 and CP1 contain the exchanged data: CP0 transfers data from the transceiver

to the Neuron Chip, and CP1 transfers data from the Neuron Chip to the transceiver.

The Neuron Chip and transceiver continuously exchange data through its CP0 and CP1 pins.

The bit clock defines transitions between bits in the data stream. The Neuron Chip uses the

falling edge of the bit clock to both sample CP0 and change CP1 to the next bit. The

transceiver should use the rising edge of bit clock to sample CP1 and update CP0.

The serial data streams on CP0 and CP1 are divided into 16-bit frames. The frame clock

(CP4) is used to define the boundaries of the frames. The frame clock is active (high) while

the Neuron Chip is outputting the least-significant bit (LSB) of the frame on CP1. On the

falling edge of the frame clock, the Neuron Chip is sampling the most-significant bit (MSB) of

the next frame on CP0.

The first eight bits of each frame are interpreted as the status field and the last eight bits as

the data field. The status field controls transceiver operation and controls passing data

between the Neuron Chip and the transceiver. The interpretation of each status bit is shown

Series 6000 Chip Data Book

51