Memory architecture – Echelon Series 6000 Chip databook User Manual

Page 35

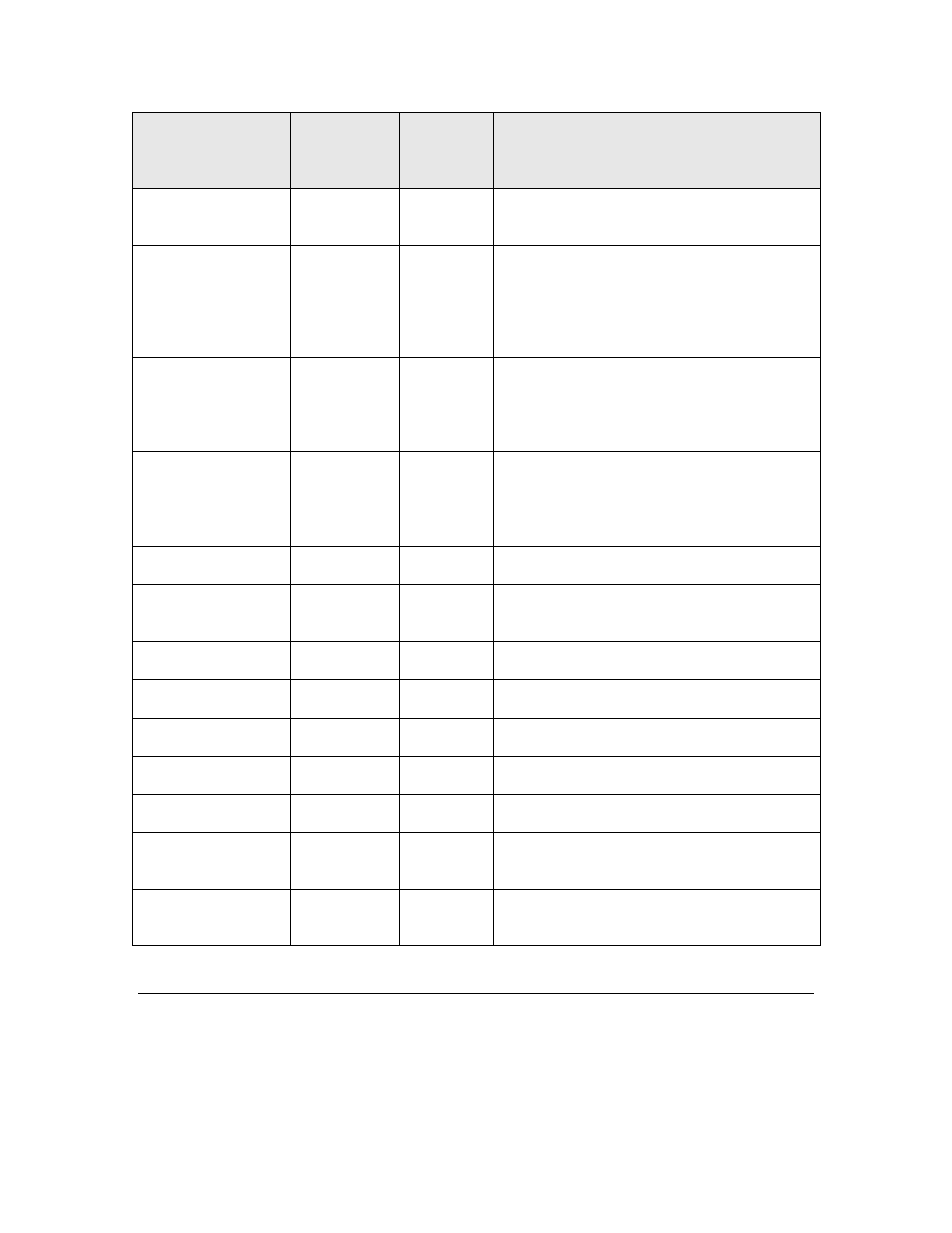

Instruction

Instruction

Size

(Bytes)

CPU

Cycles

Required Description

SHLA

SHRA

1

2

Signed left shift TOS into carry

Signed right shift TOS into carry

ADD

AND

OR

XOR

ADC

1

4

Operate with NEXT on TOS, drop NEXT

ADD #literal

AND #literal

OR #literal

XOR #literal

2

3

Operate with literal on TOS

ADD_R

AND_R

OR_R

XOR_R

1

7

Operate with NEXT on TOS, drop NEXT

and return

ALLOC #literal

1

3

Add [1 to 8] to data stack pointer

DEALLOC_R

#literal

1

6

Subtract [1 to 8] from data stack pointer

and return

SUB NEXT,TOS

1

4

TOS = NEXT – TOS, drop NEXT

SBC NEXT, TOS

1

4

TOS = NEXT – TOS – carry, drop NEXT

SUB TOS,NEXT

1

4

TOS = TOS – NEXT, drop NEXT

XCH

1

4

Exchange TOS and NEXT

INC [PTR]

1

6

Increment 16-bit pointer [0 to 3]

DIV

1

14

Divide NEXT by TOS, quotient is in TOS,

remainder is in NEXT

MUL

1

14

Multiply NEXT * TOS, result is in TOS,

NEXT

Memory Architecture

The memory architecture for a Series 6000 chip includes on-chip memory and off-chip non-

volatile memory. Every Series 6000 device must have at least 512 KB of off-chip memory

available in an SP1 flash device.

Series 6000 Chip Data Book

23