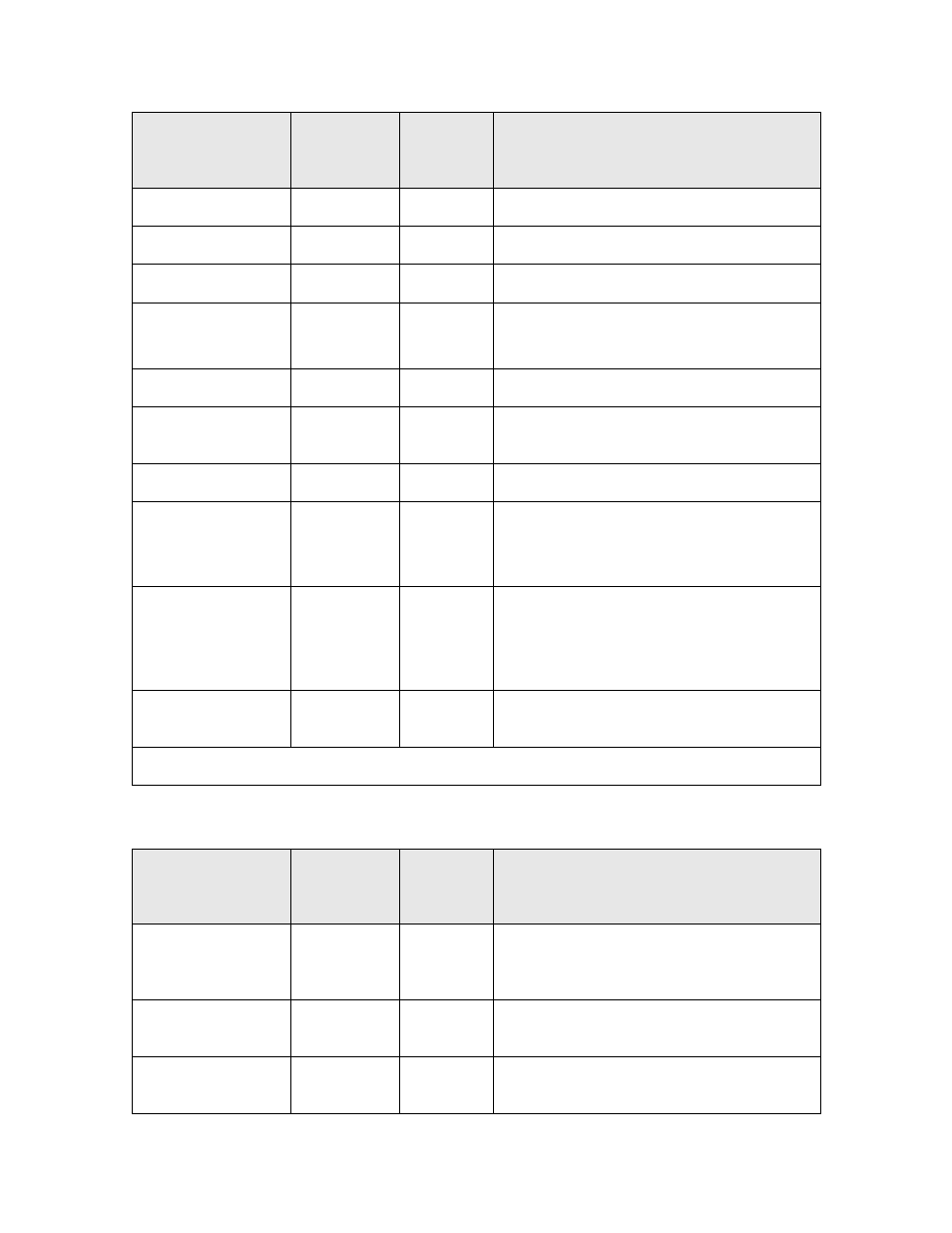

D table 10 – Echelon Series 6000 Chip databook User Manual

Page 34

Instruction

Instruction

Size

(Bytes)

CPU

Cycles

Required Description

PUSH #literal

2

4

Push 8-bit literal value [0 to 255]

PUSHPOP

1

5

Pop from return stack, push to data stack

POPPUSH

1

5

Pop from data stack, push to return stack

PUSH [DSP][-D]

POP [DSP][-D]

1

5

Push / pop DSP modified by D

EA = BP + DSP – displacement [1 to 8]

PUSHD #literal

3

6

Push 16-bit literal value, high byte first

PUSHD [PTR]

1

6

Push from 16-bit pointer [0 to 3], high byte

first

POPD [PTR]

1

6

Pop to 16-bit pointer [0 to 3], low byte first

PUSH [PTR][TOS]

POP [PTR][TOS]

1

6

Push / pop 16-bit pointer [0 to 3], modified

by TOS

EA = (16-bit pointer) + TOS.

PUSH [PTR][D]

POP [PTR][D]

2

7

Push / pop 16-bit pointer [0 to 3], modified

by D

EA = (16-bit pointer) + displacement [0 to

255]

PUSH absolute

POP absolute

3

7

Push / pop absolute memory address

Note: EA = Effective Address.

Table 10. Arithmetic and Logic Instructions

Instruction

Instruction

Size

(Bytes)

CPU

Cycles

Required Description

INC

DEC

NOT

1

2

Increment TOS

Decrement TOS

Negate TOS

ROLC

RORC

1

2

Rotate left TOS through carry

Rotate right TOS through carry

SHL

SHR

1

2

Unsigned left shift TOS, clear carry

Unsigned right shift TOS, clear carry

22

Hardware Resources