Shared – Echelon Series 6000 Chip databook User Manual

Page 30

Register

Size (Bits)

Contents

BP

16

Address of 256-Byte Base Page

DSP

8

Data Stack Pointer within Base Page

RSP

8

Return Stack Pointer within Base Page

TOS

8

Top of Data Stack, ALU Input

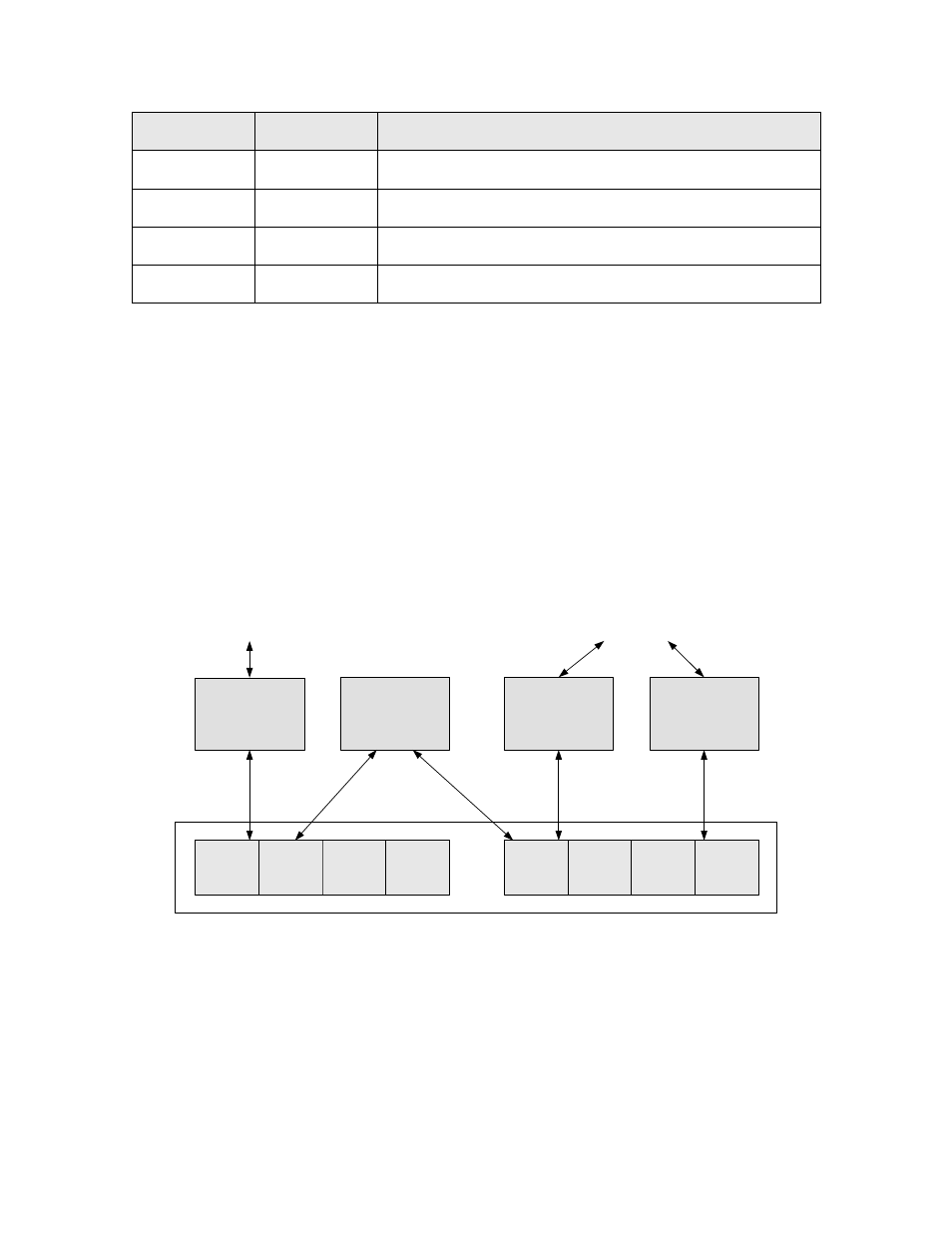

Processor 1 is the MAC layer processor that handles layers 1 and 2 of the seven-layer

LonTalk

®

protocol, which includes driving the communications subsystem hardware and

running the media access control algorithm. The MAC processor communicates with the

NET processor using network buffers located in shared RAM memory, as shown in Figure 5.

Processor 2 is the network processor that implements layers 3 through 6 of the LonTalk

protocol. The NET processor handles network variable processing, addressing, transaction

processing, authentication, background diagnostics, software timers, network management,

and routing functions. The NET processor uses network buffers in shared memory to

communicate with the MAC processor, and application buffers to communicate with the APP

processor. These buffers are also located in shared memory (RAM). Access to the shared

memory is mediated with hardware semaphores to resolve contention when updating shared

data.

Processor 3 is the application processor. The APP processor executes the user-written code,

together with the system services called by user code.

MAC

Processor

Network

Processor

Application

Processor

Interrupt

Processor

Shared

Network Buffers

Application Buffers

Communications

Port

Input/Output

Figure 5. Processor Shared Memory Allocation

18

Hardware Resources