Echelon Series 6000 Chip databook User Manual

Page 59

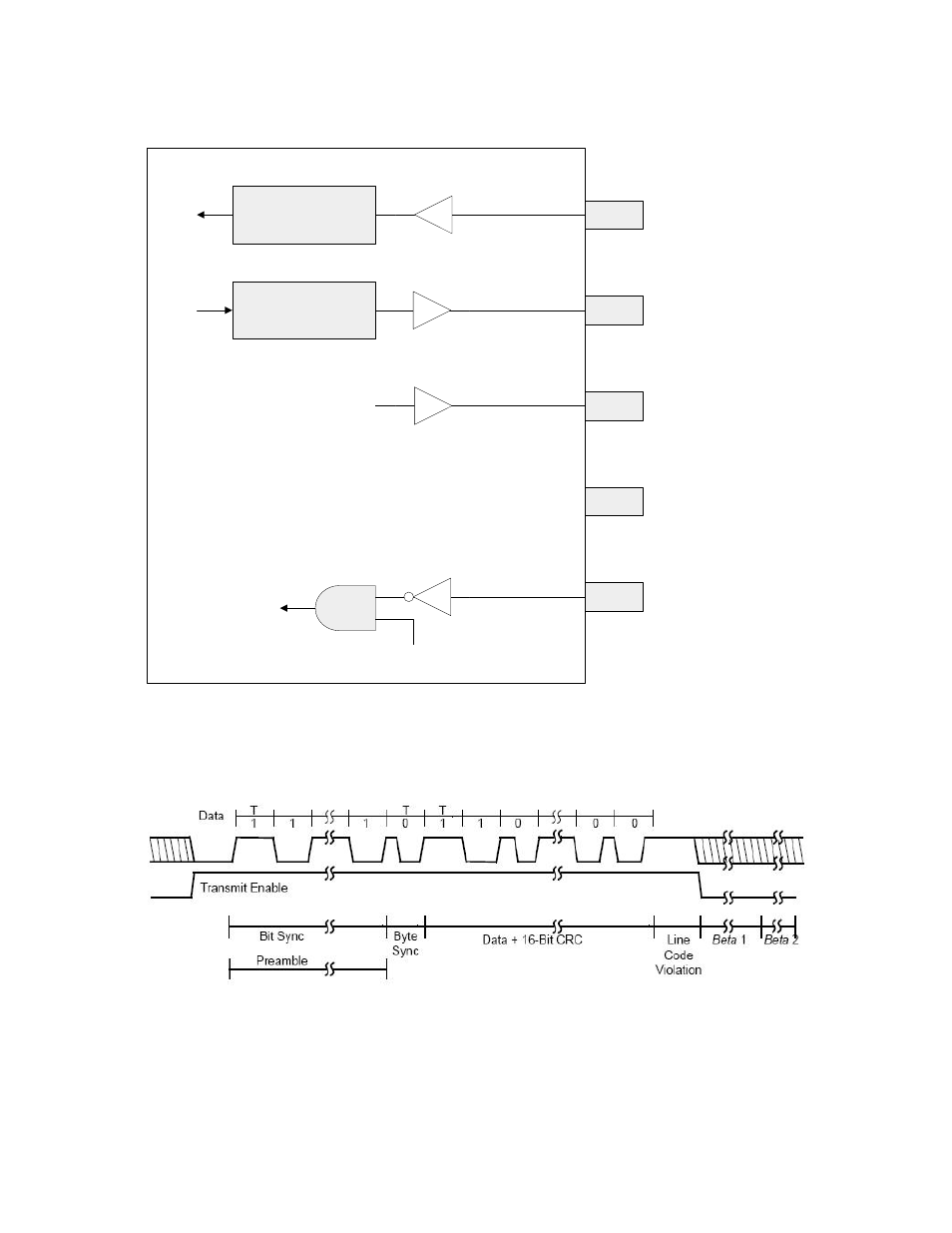

CP0

CP1

CP2

CP3

CP4

TransmitEnable

Neuron 6000 Processor

Data Input

Data Output

Transmit Enable Output

CollisionDetect~ Input

Differential Manchester

Decoder

Differential Manchester

Encoder

CollisionDetectEnable

NRZ

Data

NRZ

Data

Do Not Connect

CollisionDetect

Figure 16. Single-Ended Mode Configuration

Figure 17 shows a typical packet, where T is the bit period, equal to 1/(bit rate). Clock

transitions occur at the beginning of a bit period, and therefore, the last valid bit in the

packet does not have a trailing clock edge.

Figure 17. Single-Ended Mode Data Format

Before beginning to transmit the packet, the Neuron Chip initializes the output data pin to

start low. It then asserts the Transmit Enable pin (CP2) to ensure that the first transition in

the packet is from low to high. This first transition occurs within 1 bit time of asserting

Transmit Enable, and marks the beginning of the packet.

Series 6000 Chip Data Book

47