Eia-485 transceivers – Echelon Series 6000 Chip databook User Manual

Page 70

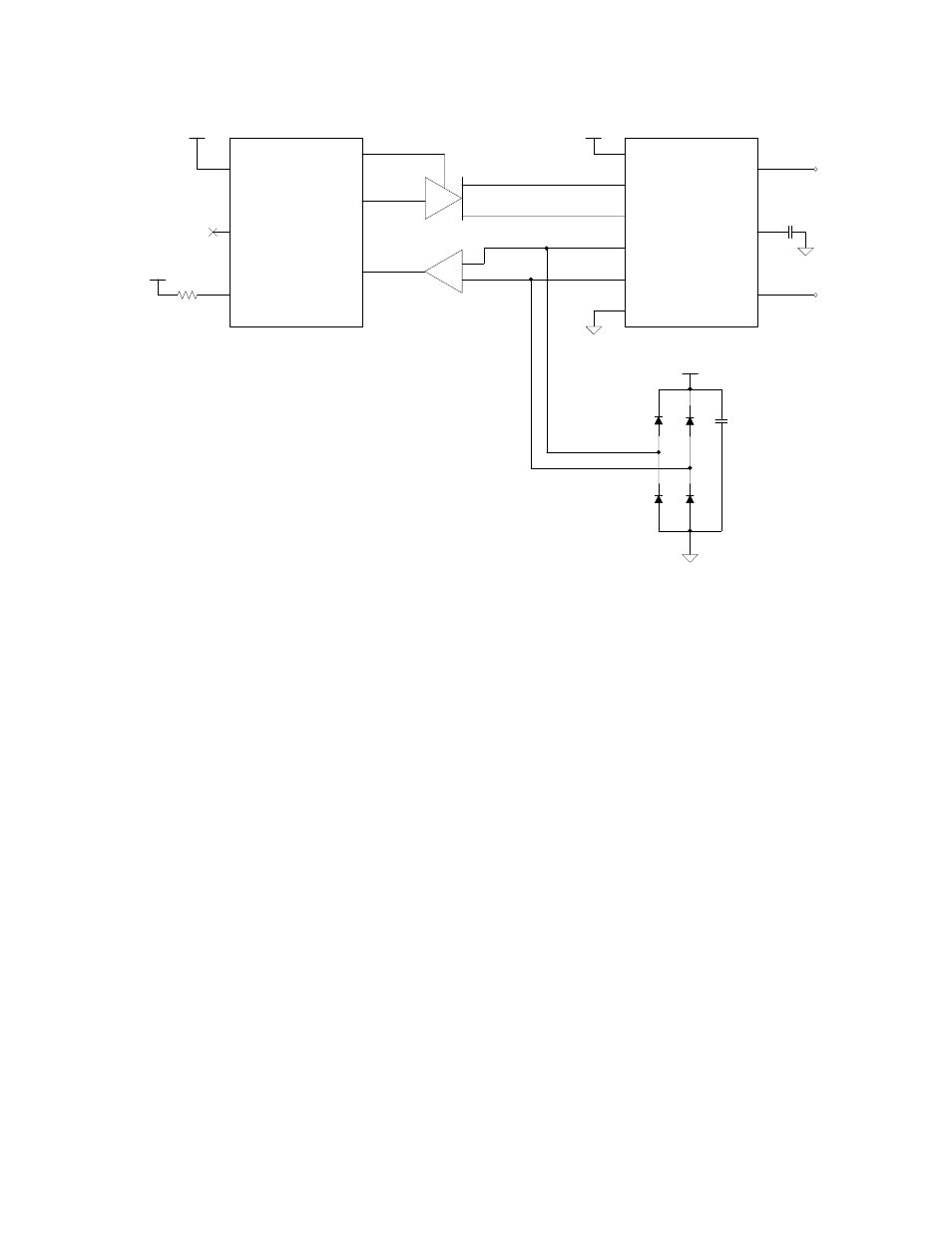

CP2

CP1

CP4

CP3

CP0

DATA_B

DATA_A

CP3

CP2

GND

VDD5

CP0

CP1

2

5

4

3

9

7

6

1

37 TXEN

34 TX

39

38

32 RX

Neuron 6000 Processor

TPT/XF-1250

3.3 V Single-Ended Mode

+5 V

VDD3V3

+3.3 V

8

8

CT

NET1

NET2

+3.3 V

Differential Driver

Circuit

Comparator

Circuit

10k

+3.3 V

0.1 µF

+5 V

Figure 21. Connecting a Neuron 6000 Processor to a TP/XF-1250 Transceiver

In the figure, the pullup resistor for the Neuron Chip’s CP4 pin is optional, but helps prevent

contention on the CP4 pin if the Neuron Processor is incorrectly configured to operate in

special-purpose mode (for which the CP4 pin is an output). The diode clamps for the

TPT/XF-1250 transceiver’s CP0 and CP1 signals are high-speed switching diodes, such as

Fairchild Semiconductor

®

1N4148 small-signal diodes. The value of the capacitor on the

TPT/XF-1250 transceiver’s transformer center tap (CT) pin depends on the device’s PCB

layout and EMI characteristics. A typical value is 100 pF rated for 1000 V. For more

information about the TPT/XF-1250 transceiver, see the L

ON

W

ORKS

TPT Twisted Pair

Transceiver Module User’s Guide (078-0025-01C).

The details of the required differential driver circuit and the comparator circuit for the

Neuron 5000 or Neuron 6000 are described in the Connecting a Neuron 5000 Processor to an

External Transceiver Engineering Bulletin (005-0202-01B).

EIA-485 Transceivers

You can use the Neuron 6000 Processor with commercially available EIA-485 transceivers.

Multiple data rates (up to 1.25 Mbps), and a number of wire types can be supported. With an

EIA-485 transceiver, common-mode voltage ranges between –7 V to +12 V. To implement an

EIA-485 device, the Neuron 6000 Processor’s communications port runs in single-ended

mode.

Available industry standards that describe EIA-485 specifications provide details on unit

loads, data rate, wire size, and wire distances. To ensure interoperability between devices,

the L

ON

M

ARK

interoperability guidelines require a data rate of 39 kbps for devices that use

EIA-485 transceivers. In addition, the EIA-485 transceiver must have TTL-compatible

58

Hardware Resources