Echelon Series 6000 Chip databook User Manual

Page 79

and firmware initialization before executing application programs, including the following

tasks:

•

The ROM system image is copied from ROM to RAM (approximately 43 ms)

•

The three base processors (NET, MAC, and APP) start running and the ROM system

image starts running

•

The ROM system image discovers the external FLASH boot loader image and loads it

over the original ROM system image in RAM (approximately 260 ms). The three base

processors restart and execute the boot loader.

•

The FLASH boot loader adjusts the system clock to 80MHz and proceeds to load the

FLASH system image over the boot loader image in RAM (approximately 90ms). The

three base processors restart and execute the system image. The built-in self test

(BIST) executes, testing the timer/counter logic, and the counter logic.

•

The application data in FLASH is shadowed to RAM. This is a 3-step process

(network image, NVM data, application code and constant data) which is at a

minimum 10 ms with a maximum of about 100 ms based on the size of the NVM data

and resident application data

•

The SVC~ pin is initialized, turning off the SVC~ pin (high state)

•

The system clock is set to the rate specified in the configuration data

•

The extended RAM is initialized based on the information contained in the

configuration data

•

The communication port is initialized

•

The state is initialized and a checksum is performed for the application

•

The scheduler is initialized

Approximately 10 µs after the RST~ pin is released, the Neuron Core starts running. The

SVC~ pin oscillates between a solid low and a weak pullup. Once the network image is

loaded the SVC~ pin is configured to no longer oscillate. After approximately one second the

SVC~ pin is configured to reflect the application state of the device.

The period between the RST~ pin being released and the start of the scheduler initialization

task can be between 400 ms to 500 ms. Once the scheduler initialization task starts the

network processor is available to accept incoming packets and the application may start.

If the BIST self-test fails, the device goes offline, the service LED comes on solid, and an

error is logged in the device’s status structure.

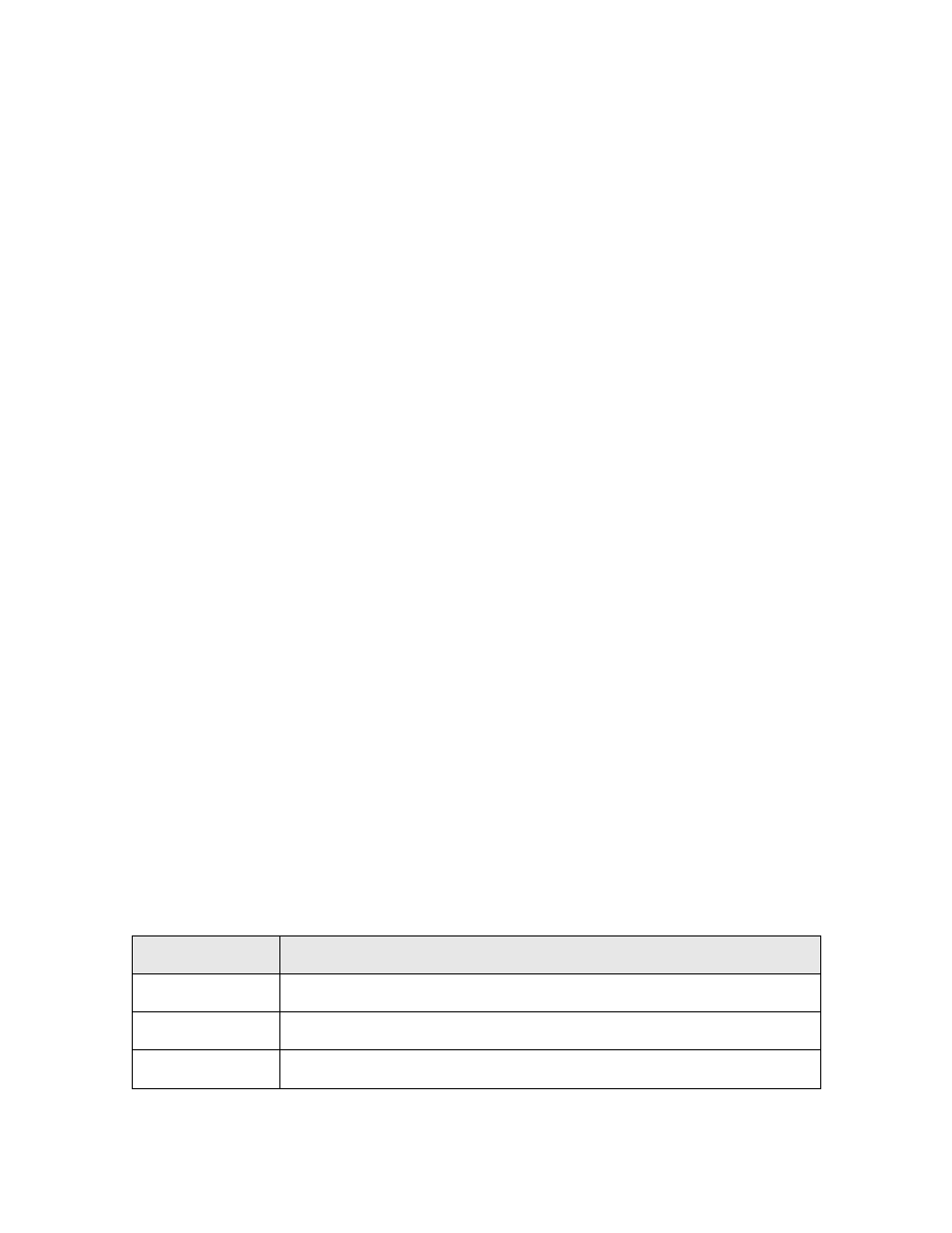

Self-test results are available in the first byte of RAM (0xE800), as listed in Table 22.

Table 22. Self-Test Results

Value

Description

0

No Failure

2

Timer/counter failure

3

Counter failure

Series 6000 Chip Data Book

67