Multiple processors – Echelon Series 6000 Chip databook User Manual

Page 29

1. Incrementing RSP

2. Moving the contents of (BP+RSP) to the low byte of the IP register

3. Incrementing RSP

4. Moving the contents of (BP+RSP) to the high byte of IP

The primary programming language used for applications is the Neuron C language, which

is a derivative of the ANSI C language that has been optimized and enhanced for L

ON

W

ORKS

distributed control applications. The major enhancements include:

•

A network communication model, based on functional blocks and network variables,

that simplifies and promotes data sharing between like and disparate devices.

•

A network configuration model, based on functional blocks and configuration

properties, that facilitates interoperable network configuration tools.

•

A type model based on standard and user resource files that expands the market for

interoperable devices by simplifying the integration of devices from multiple

manufacturers.

•

An extensive set of I/O models that support the I/O capabilities of Neuron Chips and

Smart Transceivers.

•

Powerful event-driven programming extensions, based on when statements, that

provide easy handling of network, I/O, and timer events.

•

A high-level programming model that supports application-specific interrupt

handlers and synchronization tools.

See the Neuron C Programmer’s Guide for more information about the Neuron C

programming language. The support for these capabilities is part of the Neuron firmware,

and does not need to be written by the programmer.

Multiple Processors

The Neuron core is composed of four independent logical processors:

•

Processor 1 is the Media Access Control (MAC) processor

•

Processor 2 is the network (NET) processor

•

Processor 3 is the application (APP) processor

•

Processor 4 is the interrupt (ISR) processor

The interrupt processor is only available for system clock rates of 20 MHz and higher. At the

two lower system clock rates, interrupts are handled by the application processor. See

Interrupts for more information about interrupts.

The processors share a common memory, arithmetic-logic unit (ALU), and control circuitry.

Each processor has its own set of registers, as listed in Table 7.

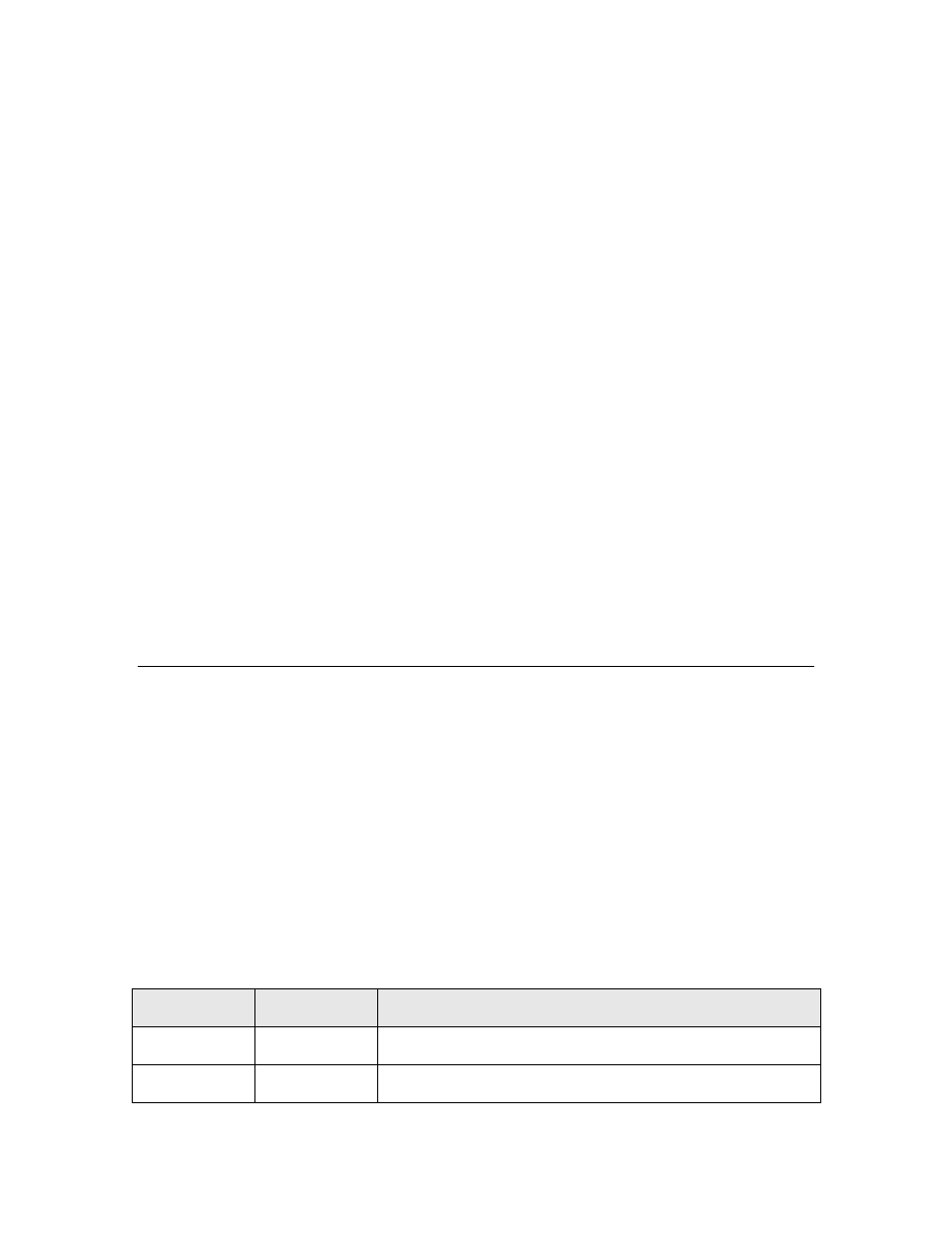

Table 7. Register Set

Register

Size (Bits)

Contents

FLAGS

8

Carry Bit and reserved internal flags

IP

16

Next Instruction Pointer

Series 6000 Chip Data Book

17