Echelon Series 6000 Chip databook User Manual

Page 165

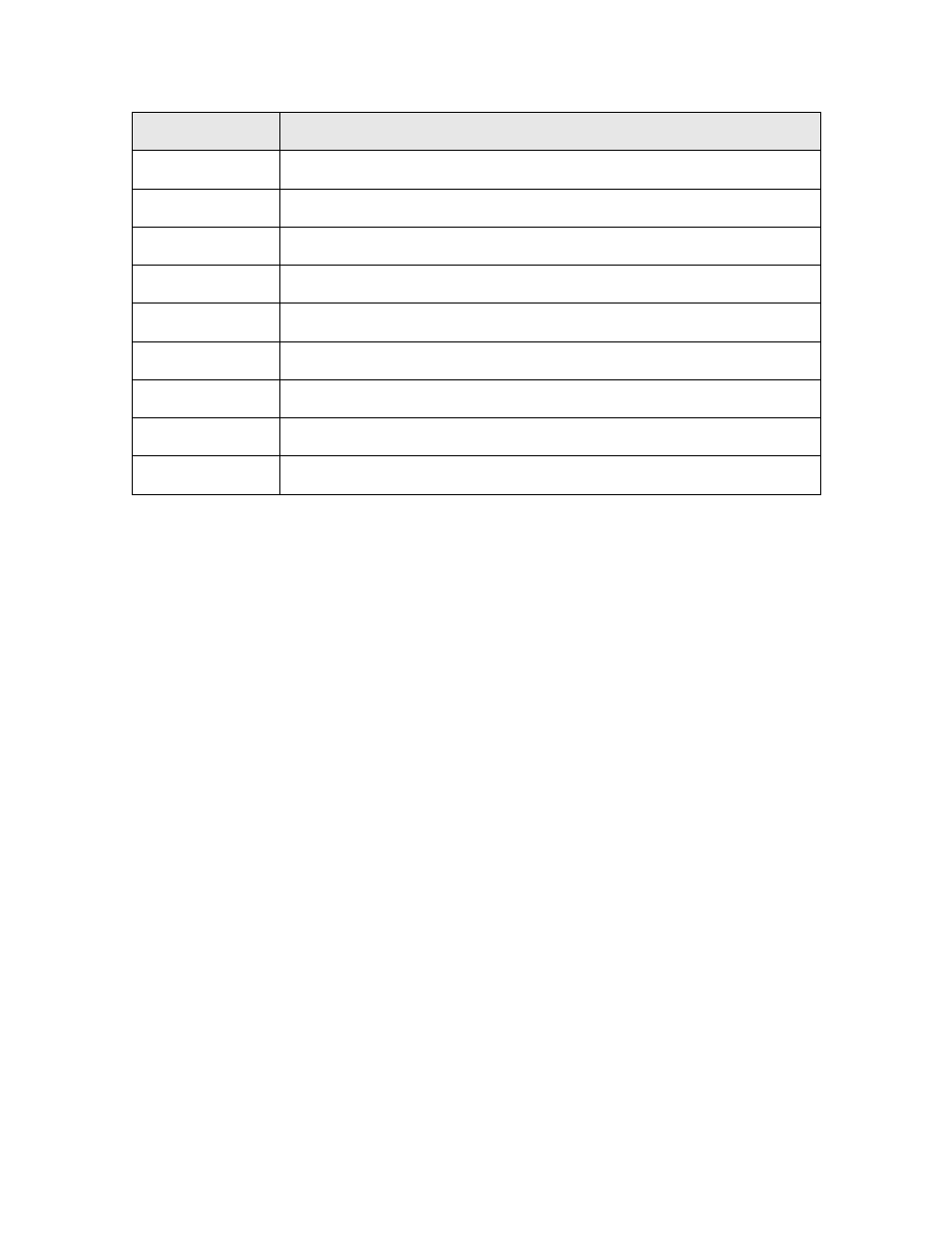

Reference

Part

C12

1.0 µF for pin 27 VOUT1V8

C16

0.01 µF across pins 25 and 26 (VDDPLL and GNDPLL)

C17

0.1 µF for pin 16 VDD1V8

C18

0.1 µF for pin 18 VDD3V3

C23

30 pF for pin 23 XIN

C24

30 pF for pin 24 XOUT

R19

200 Ω for pin 24 XOUT

R61

1 MΩ across pins 23 and 24 (XIN and XOUT)

Y1

External 10 MHz crystal

Key Layout Rules:

1. If possible, use 4-layer boards (or boards with more than four layers). Additional

layers simplify the layout, and reduce noise-related and grounding problems.

2. For 2-layer boards, the four bypass capacitors must be close to the Series 6000 chip.

V

DD

and ground must use large traces to reduce inductance and noise.

3. On 2-layer boards, avoid running high-frequency digital signal traces under the

crystal circuit or the communications port, on opposite sides of the board.

4. Ensure that power supply and ground traces are large enough to handle the peak

surge switching currents. Otherwise, there can be power supply dips on the V

DD

pins, which could cause errors in the checksum calculation, resulting in the Series

6000 chip’s resetting.

Series 6000 Chip Data Book

153