Echelon Series 6000 Chip databook User Manual

Page 57

device’s external serial non-volatile memory must be loaded with the correct communications

parameters before connecting to the network.

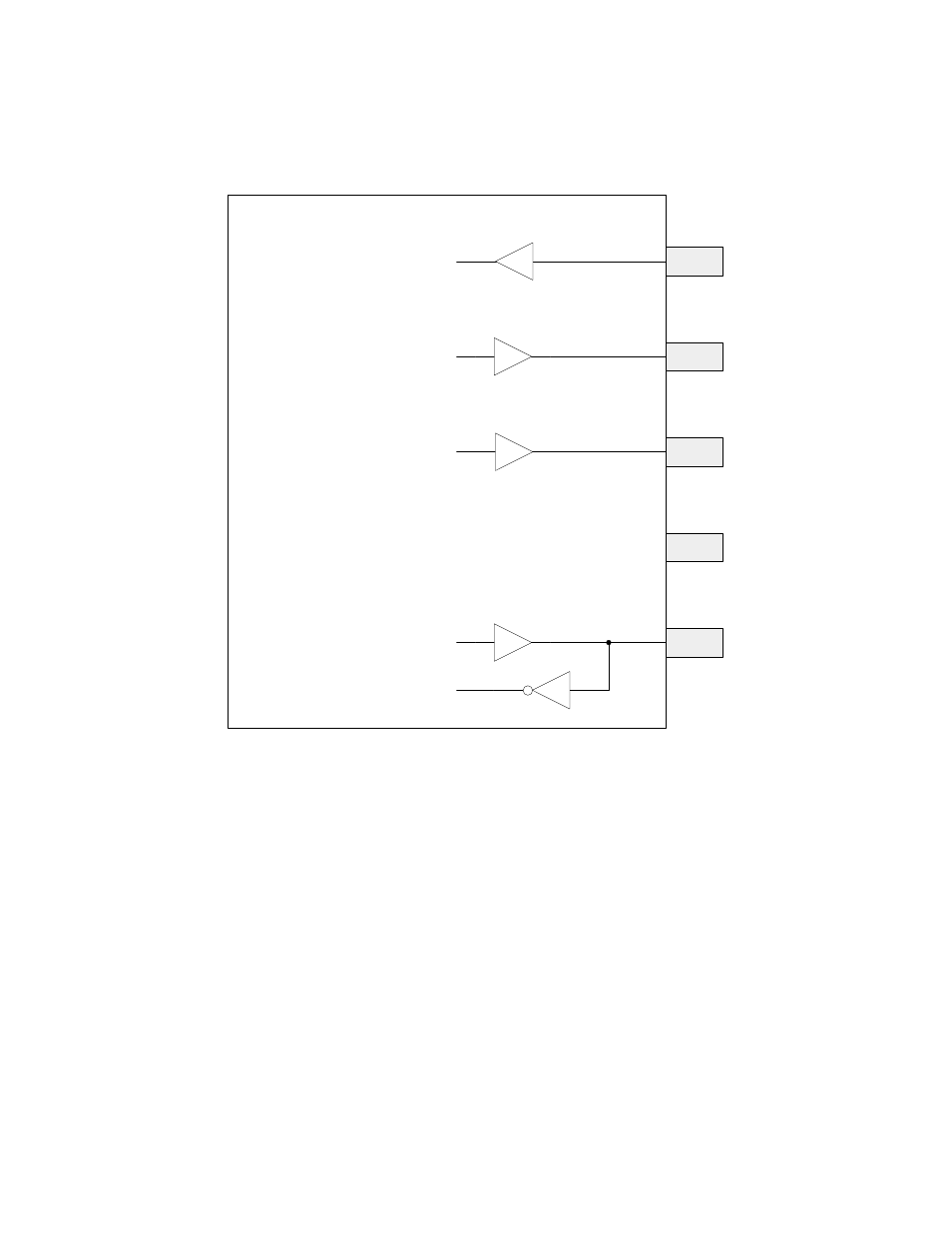

CP0

CP1

CP2

CP3

CP4

Single-Ended or Special-Purpose RX (in)

Single-Ended or Special-Purpose TX (out)

Single-Ended TX Enable or

Special-Purpose Bit Clock (out)

Frame Clock (out)

Collision Detect (in)

Neuron 6000 Processor

Figure 15. Internal Transceiver Block Diagram

Single-ended mode uses Differential Manchester encoding (also known as bi-phase space

encoding), which is a widely used and reliable format for transmitting data over various

media. This encoding scheme provides a transition at the beginning of every bit period to

synchronize the receiver clock (referred to as the clock transition). The data is indicated by

the presence or absence of a second transition (the data transition) halfway between clock

transitions. A mid-cell transition indicates a zero. Lack of a mid-cell transition indicates a

one.

The transmitter transmits a preamble at the beginning of a packet to allow the other devices

to synchronize their receiver clocks. The preamble consists of a bit-sync field and a byte-sync

field. The bit-sync field is a series of Differential Manchester ones; its duration is user

selectable, and is at least four bits long. The byte-sync field is a single bit Differential

Manchester zero that marks the end of the preamble, and the beginning of the first data byte

of the packet.

The Neuron Chip terminates the packet by forcing a Differential Manchester code violation,

that is, the Neuron Chip holds the data output transitionless long enough for the receiver to

recognize an invalid code that signals the end of transmission. The data output can be either

high or low for the duration of the line-code violation, depending on the state of the data

Series 6000 Chip Data Book

45