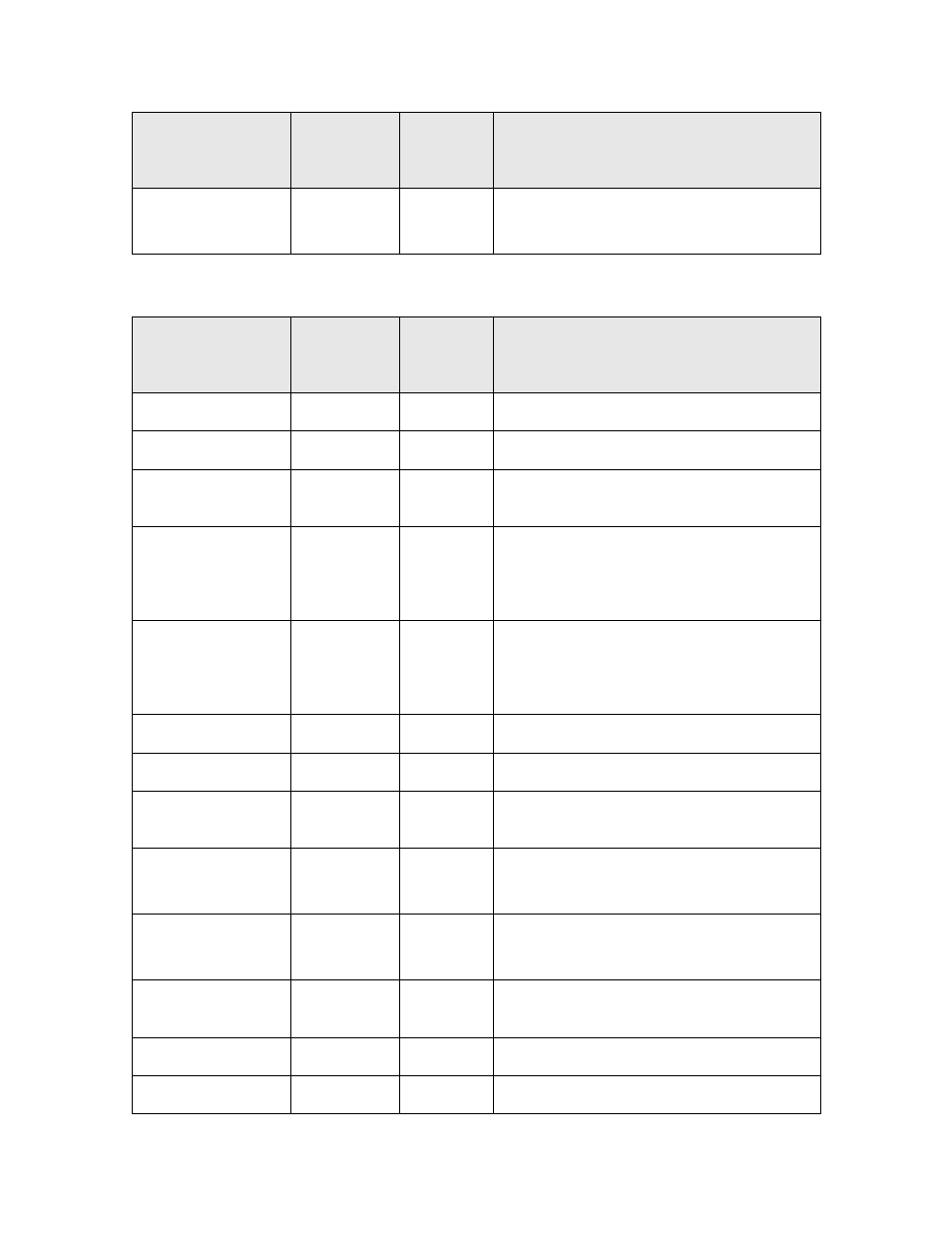

Table 9 – Echelon Series 6000 Chip databook User Manual

Page 33

Instruction

Instruction

Size

(Bytes)

CPU

Cycles

Required Description

CALLF

3

7

Call subroutine far

Pushes two bytes to return stack.

Table 9. Memory and Stack Instructions

Instruction

Instruction

Size

(Bytes)

CPU

Cycles

Required Description

PUSH TOS

1

3

Increment DSP, duplicate TOS into NEXT

DROP TOS

1

3

Move NEXT to TOS, decrement DSP

DROP_R TOS

1

6

Move NEXT to TOS, decrement DSP,

return from call

PUSH NEXT

PUSH DSP

PUSH RSP

PUSH FLAGS

1

4

Push processor register

POP NEXT

POP DSP

POP RSP

POP FLAGS

1

4

Pop processor register

DROP NEXT

1

2

Decrement DSP

DROP_R NEXT

1

5

Decrement DSP and return from call

PUSH !D

POP !D

1

4

Push / pop byte register [8 to 23]

PUSH !TOS

1

4

Push TOS

EA = BP + TOS, push byte to NEXT.

POP !TOS

1

4

Pop TOS

EA = BP + TOS, pop byte from NEXT.

PUSH [RSP]

1

4

Push from return stack to data stack, RSP

unchanged

DROP [RSP]

1

2

Increment RSP

PUSHS #literal

1

4

Push short literal value [0 to 7]

Series 6000 Chip Data Book

21