Traps, Software-controlled reset, Reset processes and timing – Echelon Series 6000 Chip databook User Manual

Page 78

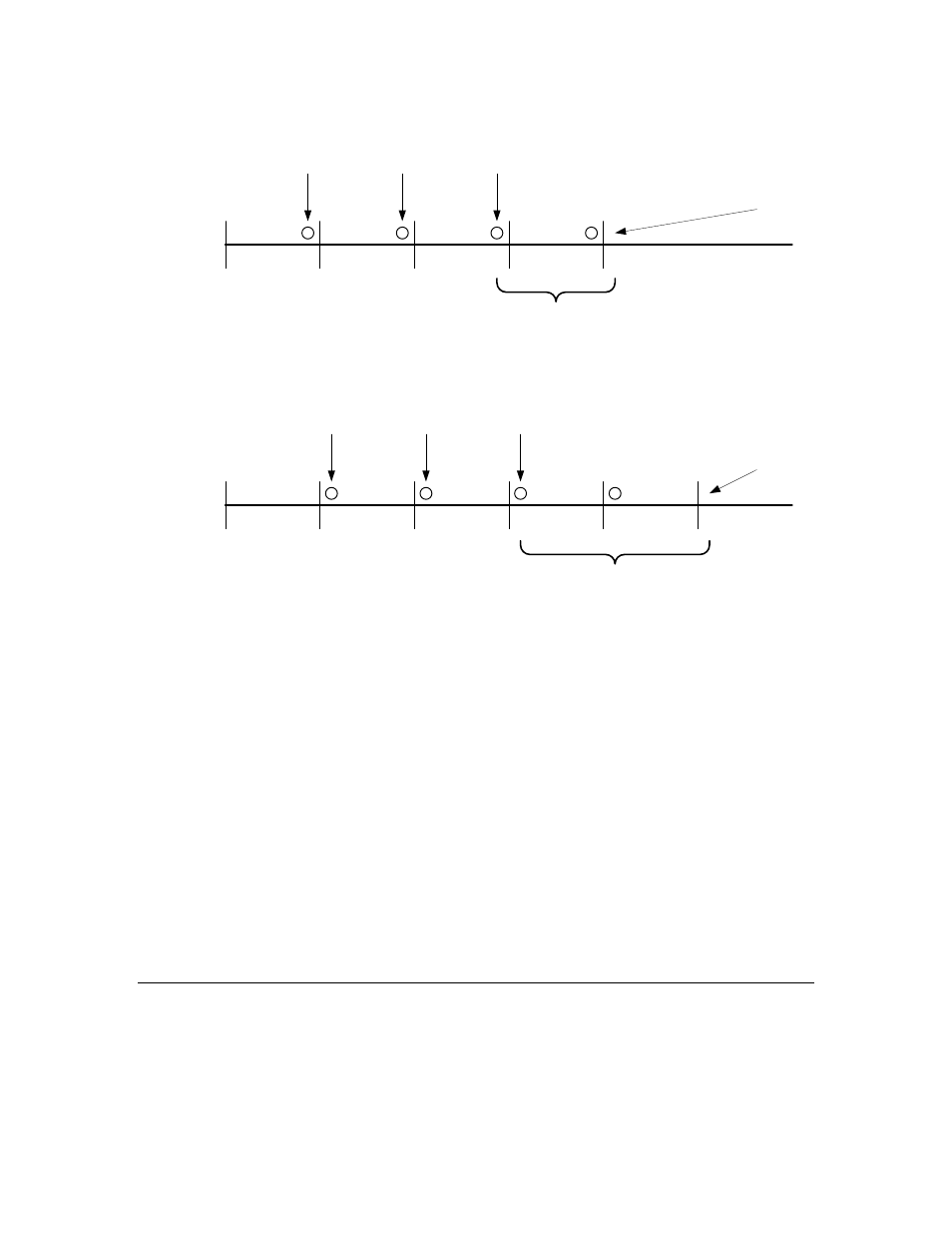

Watchdog Timer Ticks (840 ms)

Update WDT

Series 6000

Chip Resets

Update WDT

Update WDT

No Update

About 840 ms

From Last Update to Reset

Update WDT

Update WDT

Update WDT

No Update

Watchdog Timer Ticks (840 ms)

Series 6000

Chip Resets

About 1.7 s

From Last Update to Reset

EXAMPLE 1

EXAMPLE 2

A

B

C

D

A

B

C

D

Figure 27. Series 6000 Watchdog Timer Period

Because your application typically has no knowledge of the current WDT tick, the application

should update the WDT at regular intervals at least every 500 ms.

Traps

The Neuron architecture provides a set of interrupts for various error conditions that allow

the application or firmware to continue to run. A system-level trap is highest level of

interrupt and is non-maskable, that is, it cannot be disabled. For each of these traps, the

system firmware handles the interrupt, initiates a reset if necessary, and updates the error

log for the chip. See Processor Integrity for additional information about these traps.

Software-Controlled Reset

When the CPU watchdog timer expires, or a software command to reset occurs, the RST~

pin is pulled low for 100 µs.

Reset Processes and Timing

During the reset period, the I/O pins are in a high-impedance state. The SVC~ pin is high

impedance during reset with an internal pull-up resistor.

Below is a summarization of the steps that a Series 6000 chip follows in preparing to execute

application code. After the RST~ pin is released, the Series 6000 chip performs hardware

66

Hardware Resources