Echelon Series 6000 Chip databook User Manual

Page 64

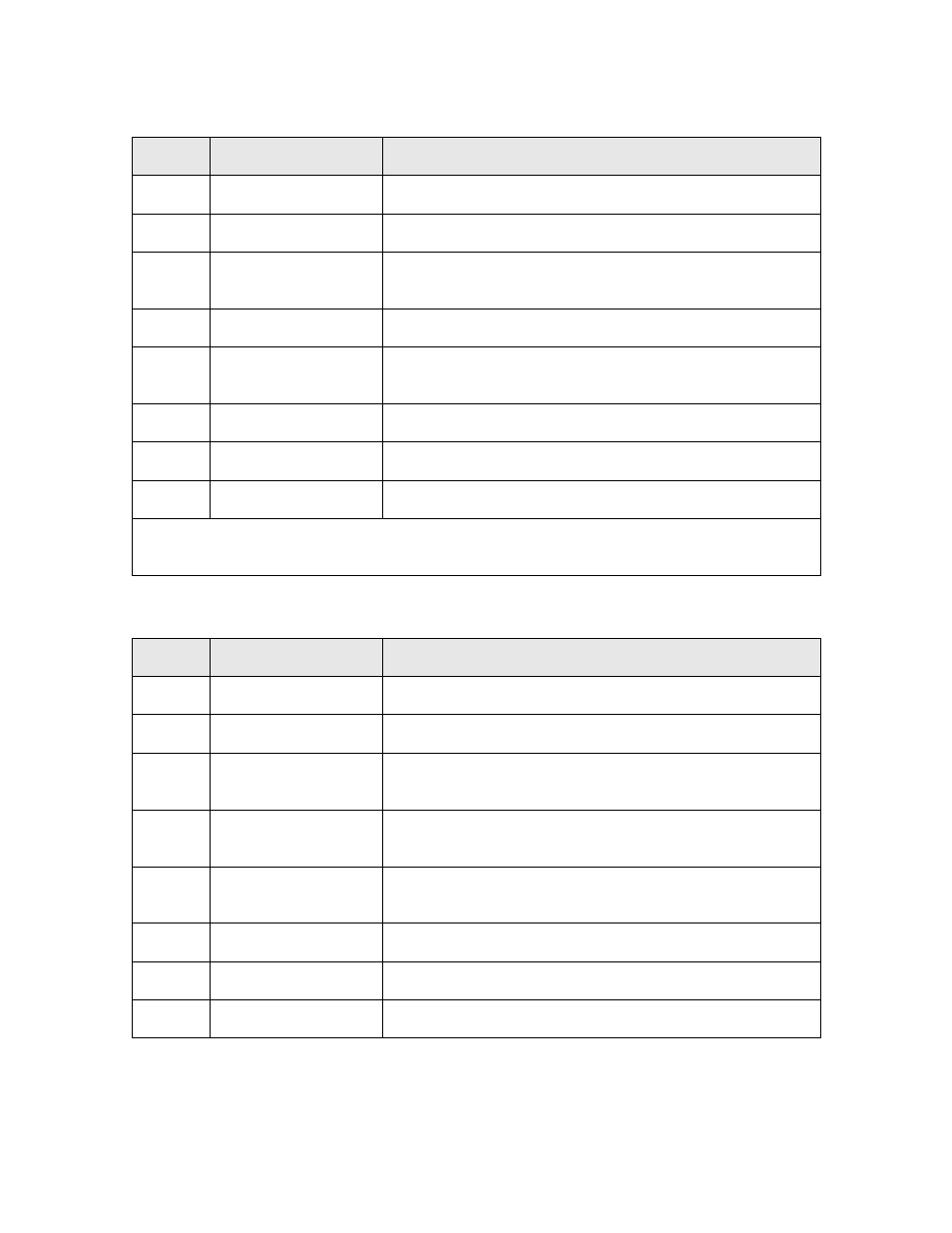

Table 19. Special-Purpose Mode Transmit Status Bits

Bit

Flag

Description

7

TX_FLAG

Neuron Chip in the process of transmitting packet

6

TX_REQ_FLAG

Neuron Chip requests to transmit on the network

5

TX_DATA_VALID

Neuron Chip is passing network data to the transceiver in

this frame

4

Don’t Care

Unused

3

TX_ADDR_R/W

If negated, Neuron Chip is writing internal transceiver

register

2

TX_ADDR_2

Address bit 2 of internal transceiver register [1..7]

1

TX_ADDR_1

Address bit 1 of internal transceiver register [1..7]

0

TX_ADDR_0

Address bit 0 of internal transceiver register [1..7]

Note: For bits [2..0] the internal transceiver register 0 is not valid. Registers [1..7] are

defined by the transceiver implementation.

Table 20. Special-Purpose Mode Receive Status Bits

Bit

Flag

Description

7

SET_TX_FLAG

Transceiver accepts request to transmit packet

6

CLR_TX_REQ_FLAG Transceiver acknowledges request to transmit packet

5

RX_DATA_VALID

Transceiver is passing network data to the Neuron Chip

in this frame

4

TX_DATA_CTS

Transceiver indicates that Neuron Chip is clear to send

byte of network data

3

SET_COLL_DET

Transceiver has detected a collision while transmitting

the preamble

2

RX_FLAG

Transceiver has detected a packet on the network

1

RD/WR_ACK

Transceiver acknowledges read/write to internal register

0

TX_ON

Transceiver is transmitting on the network

There are three types of data that can be sent and received during each frame:

1. Network packet data — Actual data (8 bits at a time) that is to be transmitted or has

been received.

52

Hardware Resources