Cyclic communication data assignment, Result data (input assemblies), Control data (output assemblies) – KEYENCE SR-750 Series User Manual

Page 97: E sr-750 um

97

E SR-750 UM

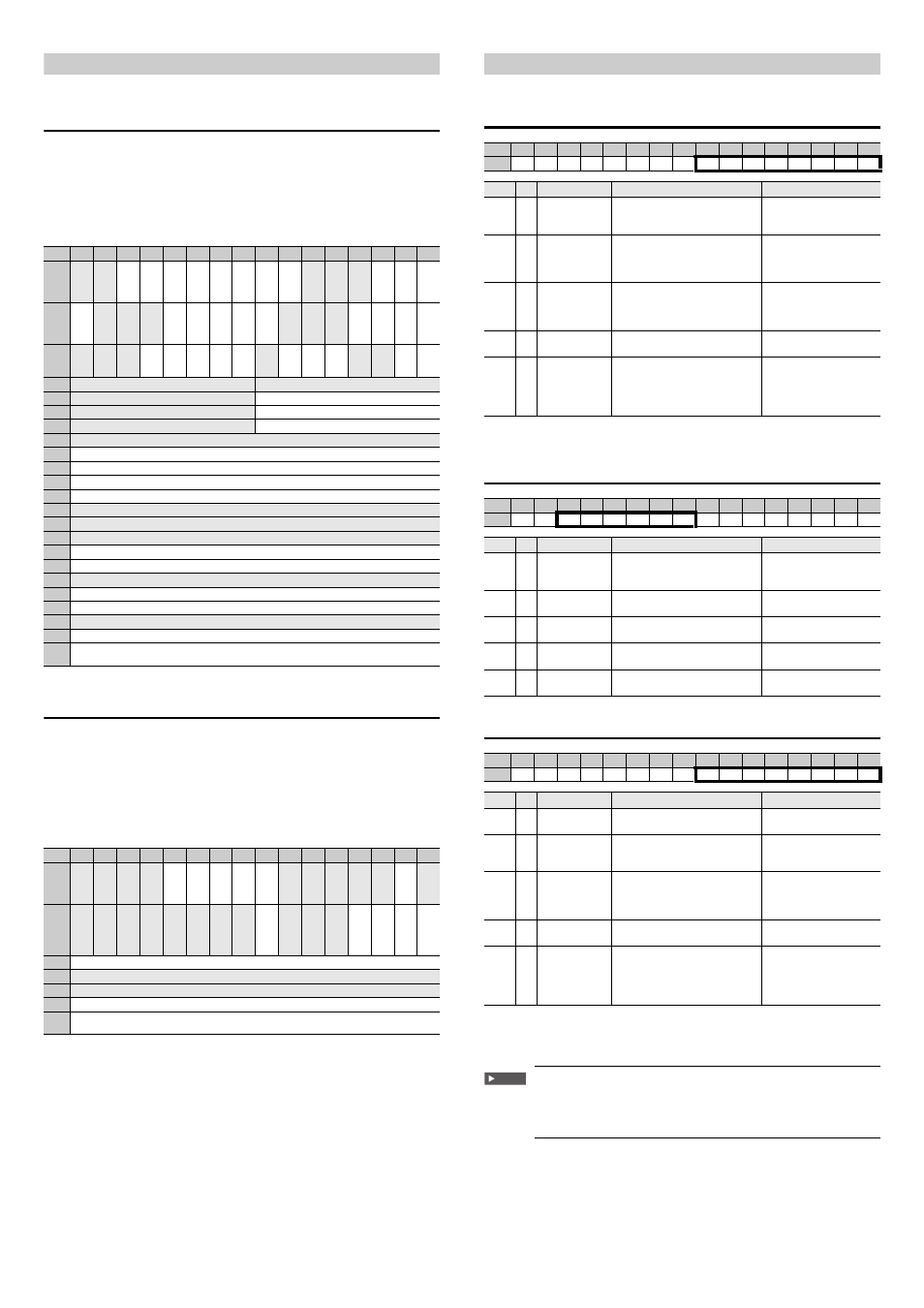

Cyclic communication data assignment

Data assignment during cyclic communication is performed as follows.

Result data (Input Assemblies)

Input Assemblies is a device that write responses from the SR-750 Series to the

PLC.

When using this device, each device function is assigned as follows.

Device status, Result Data, etc. are written to the Input Assemblies.

Input Assemblies memory map (Instance ID: 0x64)

SR-750

→ PLC

Gray parts are reserved areas for the system.

Control data (Output Assemblies)

Output Assemblies is a device that write instructions from the PLC to the SR-750

Series.

When using this device, each device function is assigned as follows.

Output Assemblies performs device control instructions, error clear, handshake

process, etc.

Output Assemblies memory map (Instance ID: 0x65)

PLC

→ SR-750

Gray parts are reserved areas for the system.

Address Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

FILE

BUSY

ERR

BUSY

MODE

BUSY

LOCK

BUSY

TRG

BUSY

BUSY

General

Error

Buffer

Overflow

Error

Read

Data

Update

Complete

Read

Data

Update

Available

Error

1

External

Instruction

Operation

Failure

Tuning

Failure

Preset Data

Registration

Failure

Preset

Reading

Failure

Reading

Error

External

Instruction

Operation

Complete

Tuning

Complete

Preset Data

Registration

Complete

Preset

Reading

Complete

Reading

Complete

2

SAE

AS9132

Unstable

AIM DPM

Unstable

ISO/

IEC15415

Unstable

Matching

Level

Unstable

Unstable

OUT3

Status

OUT2

Status

OUT1

Status

IN2

Status

IN1

Status

3

4

Matching Level

5

ISO/IEC15415 Grade

6

AIM DPM Grade

7

8

Reading Error Cause

9

Preset Reading Failure Cause

10

Preset Data Registration Failure Cause

11

Tuning Failure Cause

12

13

14

15

External Instruction Operation Error Cause

16

General Error Cause

17

18

Read Data Ready Count

19

Read Data Update Count

20

21

Read Data Size

22 and

above

Read Data

Address Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Tuning

Start

Request

Preset Data

Registration

Start

Request

Preset

Reading

Start

Request

Reading

Start

Request

Error

Clear

Transmission

Buffer Clear

Read

Data

Update

Permitted

1

External

Instruction

Operation

Complete

Clear

Tuning

Complete

Clear

Preset Data

Registration

Complete

Clear

Preset

Reading

Complete

Clear

Reading

Complete

Clear

2

Bank Number

3

4

5

Preset Data Size

6 and

above

Preset Data

Parameter details of result data (Input Assemblies)

Input Assemblies (Address 0, Bit 0 to Bit 7) Handshake

and error status

* Handshake is a communication procedure to make the permission system for

read data writing.

Input Assemblies (Address 0, Bit 8 to Bit 13) BUSY status

Input Assemblies (Address 1, Bit 0 to Bit 7) Completion status

*1 This Bit also turns ON when the character string of "ERROR" is output when

reading error occurs.

*2 This returns to 0 when turning the applicable clear Bit ON or at next operation.

Important

After "1 Preset Reading Complete", "2 Preset Data Registration

Complete" or "3 Tuning Complete", wait 5 seconds or more and

start reading operation. If reading operation starts before 5

seconds elapse, it does not operate normally.

Address Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0

Address Bit

Name

Description

Data contents

0

0

Error

This Bit turns ON when either "6

Buffer Overflow Error" or "7

General Error" Bit is ON.

0 : No error

1 : Error

0

1

Read Data

Update

Available

This Bit is used when using

handshake.

*

This displays whether read data

exists or not.

0 : No read data

1 : Read data available

0

2

Read Data

Update

Complete

This Bit is used when using

handshake.

*

This turns ON when read data

update is complete.

0

→1: Result data update

complete

0

6

Buffer Overflow

Error

This turns ON when buffer

overflow error occurs.

0 : No error

1 : Error

0

7

General Error

This turns ON when errors other

than buffer overflow error occur.

If this turns ON, the error code is

output to "Address 16 General

Error Cause".

0 : No error

1 : Error

Address Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0

Address Bit

Name

Description

Data contents

0

8

BUSY

This Bit turns ON when any of the

following BUSY Bits (9 to 13) is

ON.

0 : -

1 : BUSY status

0

9

TRG BUSY

TRG BUSY

0 : -

1 : TRG BUSY status

0

10 LOCK BUSY

LOCK BUSY

0 : -

1 : LOCK BUSY status

0

11 MODE BUSY

MODE BUSY

0 : -

1 : MODE BUSY status

0

12 ERR BUSY

ERR BUSY

0 : -

1 : ERR BUSY status

Address Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

1

Address Bit

Name

Description

Data contents

1

0

Reading

Complete

This turns ON when reading is

complete.

*1

0 : -

1 : Complete

*2

1

1

Preset

Reading

Complete

This turns ON when preset reading

is complete.

0 : -

1 : Complete

*2

1

2

Preset

Data

Registration

Complete

This turns ON when preset data

registration is complete.

0 : -

1 : Complete

*2

1

3

Tuning

Complete

This turns ON when tuning is

complete.

0 : -

1 : Complete

*2

1

7

External

Instruction

Operation

Complete

This turns ON when "Reading",

"Preset reading" or "Tuning" is

performed with the IN terminal or

command and the operation is

complete.

0 : -

1 : Complete

*2