How is sequence mode implemented – ALLIED Vision Technologies Pike F-1600 User Manual

Page 225

Controlling image capture

PIKE Technical Manual V5.1.2

225

How is sequence mode implemented?

There is a FIFO (first in first out) memory for each of the IIDC V1.31 registers

listed above. The depth of each FIFO is fixed to 32(dez) complete sets. Function-

ality is controlled by the following advanced registers.

Note

Sequence mode requires not only firmware 3.x but also special

care if changing image size, Color_Coding_ID and frame rate

related parameters. This is because these changes not only

affect settings in the camera but also require corresponding

settings in the receiving software in the PC.

Caution

Incorrect handling may lead to image corruption or loss of

subsequent images.

Please ask for detailed support when you want to use this

feature.

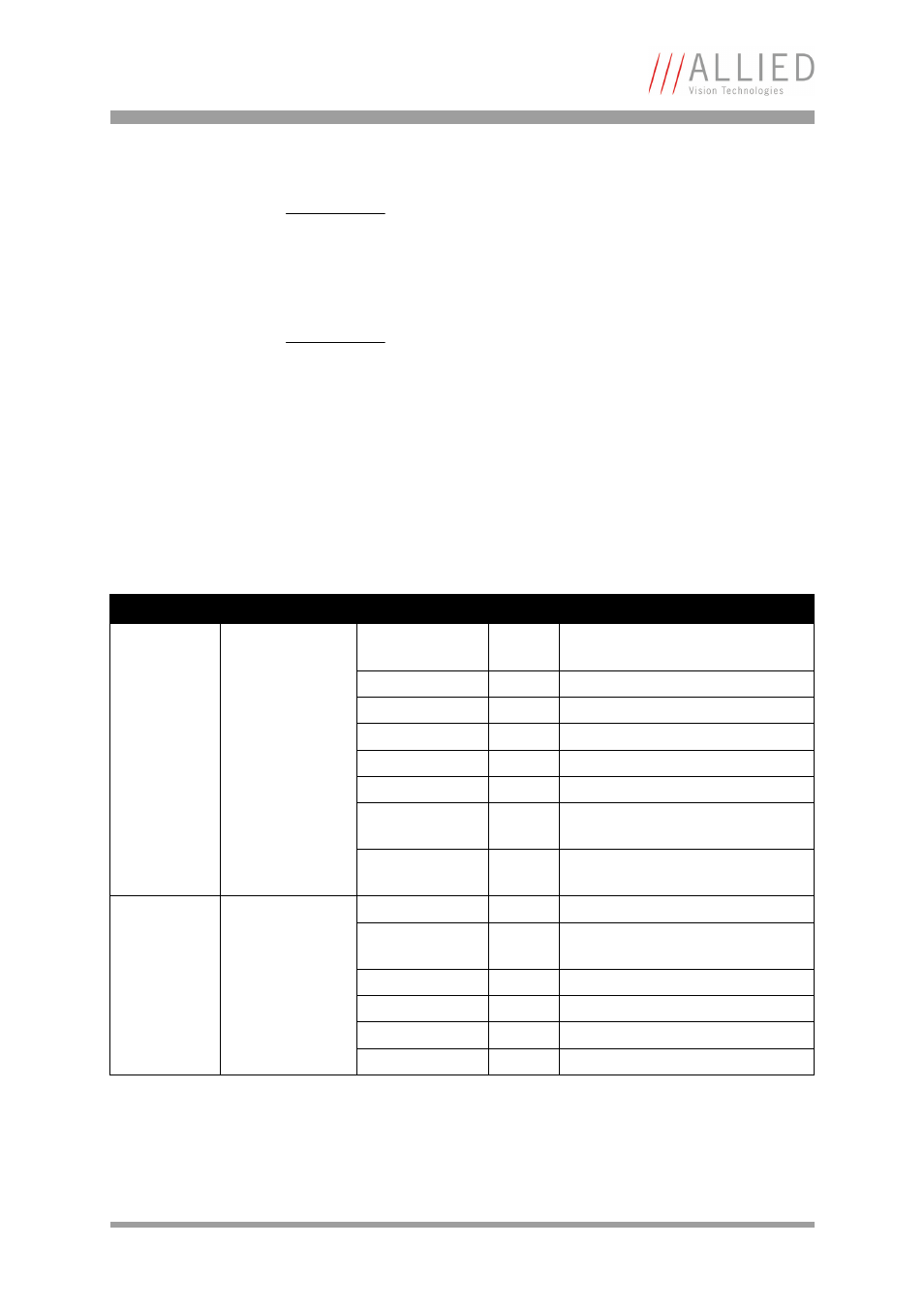

Register

Name

Field

Bit

Description

0xF1000220

SEQUENCE_CTRL

Presence_Inq

[0]

Indicates presence of this feature

(read only)

---

[1..4]

Reserved

AutoRewind

[5]

ON_OFF

[6]

Enable/disable this feature

SetupMode

[7]

Sequence setup mode

---

[8..15]

Reserved

MaxLength

[16..23] Maximum possible length of a

sequence (read only)

SeqLength

[24..31] Length of the sequence (32 dez for

all CCD models)

0xF1000224

SEQUENCE_PARAM ---

[0..4]

Reserved

ApplyParameters

[5]

Apply settings to selected image of

sequence; auto-reset

---

[6..7]

Reserved

SeqStepMode

[8..15]

Sequence stepping mode

ImageRepeat

[16..23] Image repeat counter

ImageNo

[24..31] Number of image within a sequence

Table 80: Advanced register: Sequence mode